Method and system for realizing bus connection

A bus and extended interface technology, applied in the field of bus connection, can solve the problems of high operating frequency, large delay, and timing that cannot meet the requirements of high-frequency operation, so as to avoid timing problems, ensure timing optimization, and achieve correct interaction. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

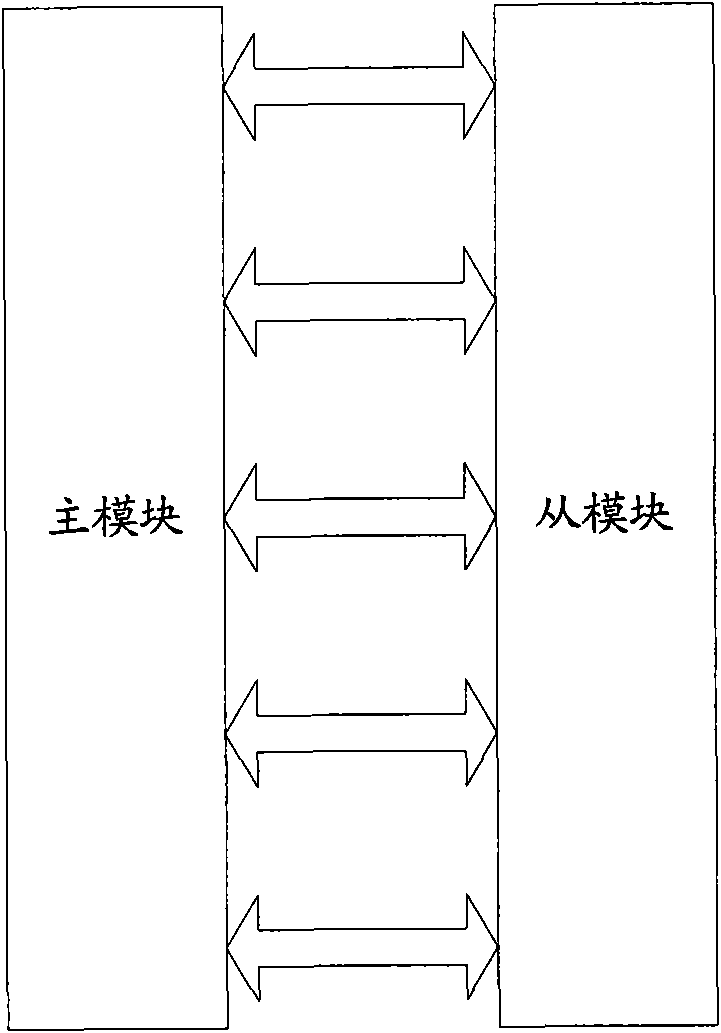

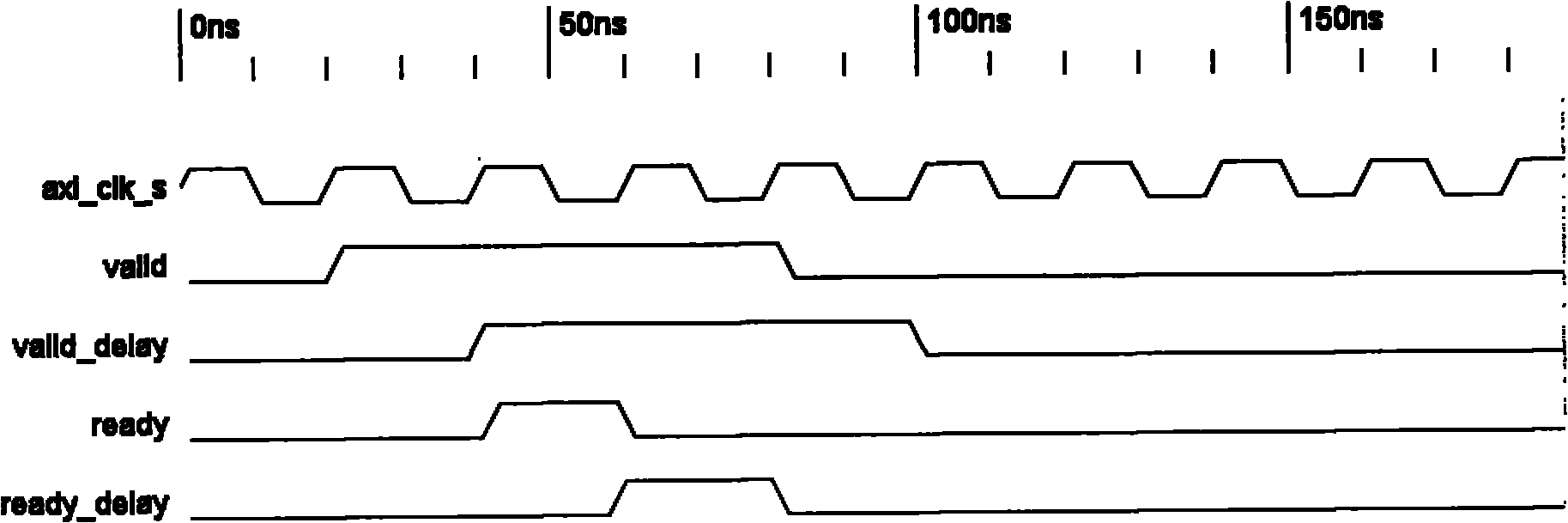

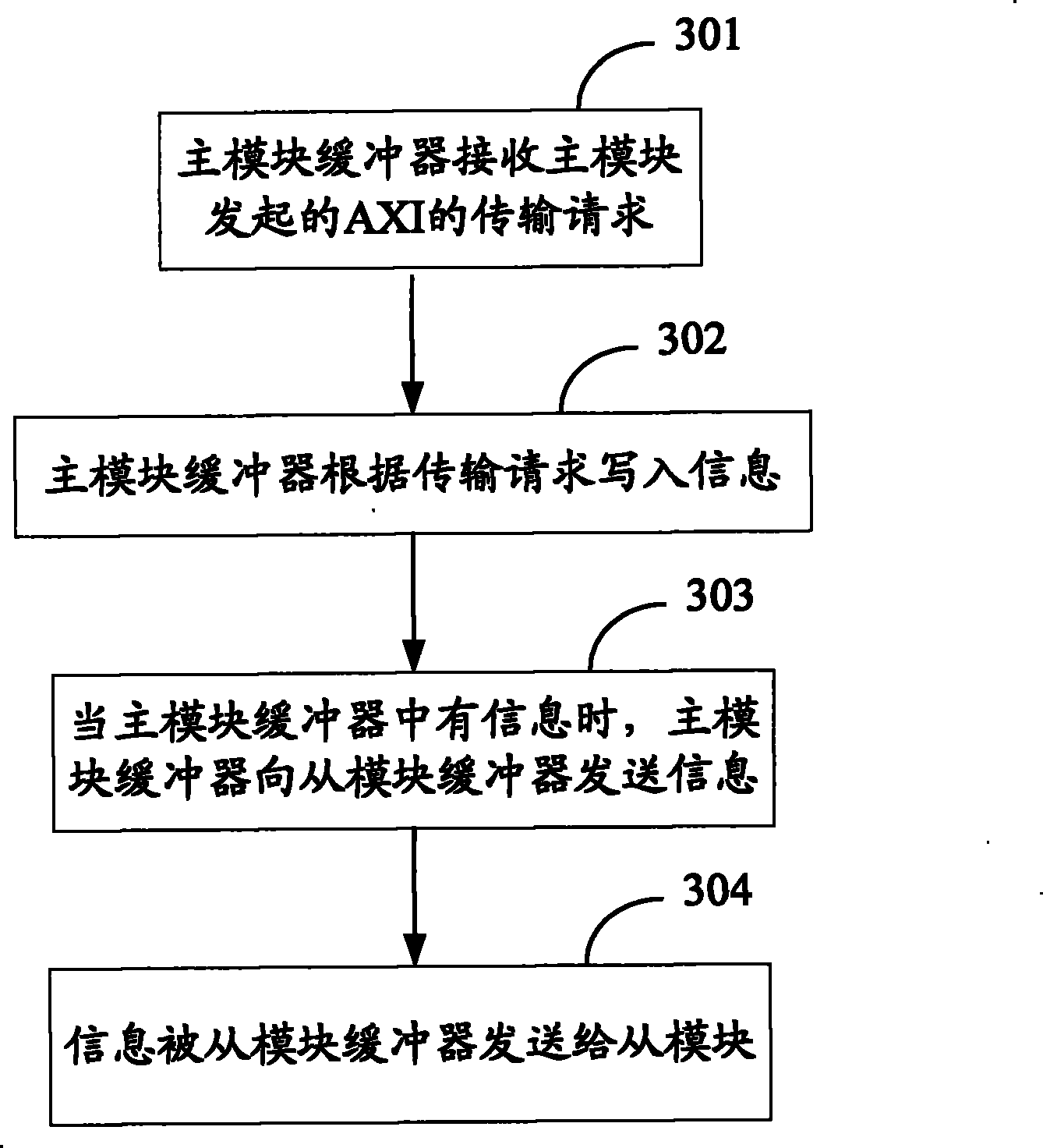

[0049] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings. figure 1 Shown is the existing AXI bus connection. Its master module (AXI MASTER) and slave module (AXI SLAVE) are directly connected, in this connection situation. If two chips or two FPGAs and an AXI bus are needed to connect between the chips and the FPGA, the delay of the PAD and the wiring may add up to a delay of more than one cycle. If the timing path between the master and slave blocks exceeds one cycle, a figure 2 error conditions that occur in . Due to the delay of more than one cycle on the connection, the valid valid signal on the master module side is sent out in the first cycle, and it will not be collected until the second cycle on the slave module side. The valid valid signal is received from the module side, the ready signal is set high, and then fed back to the main module side, it takes the third cycle to be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com