NAND flash controller circuit of multi-channel shared data cache region

A data cache area and data sharing technology, which is applied in the direction of digital memory information, static memory, instruments, etc., can solve the problem of large area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

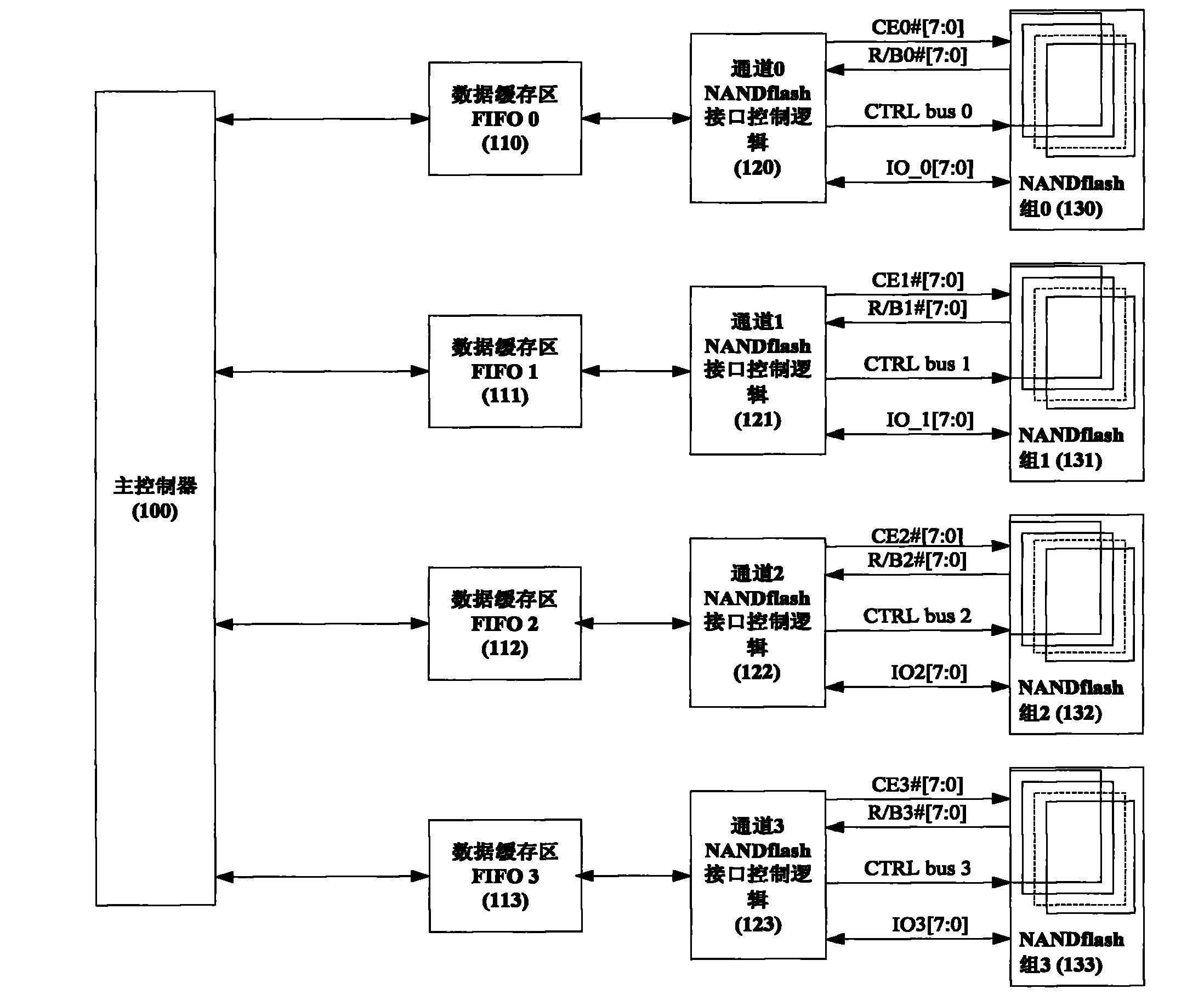

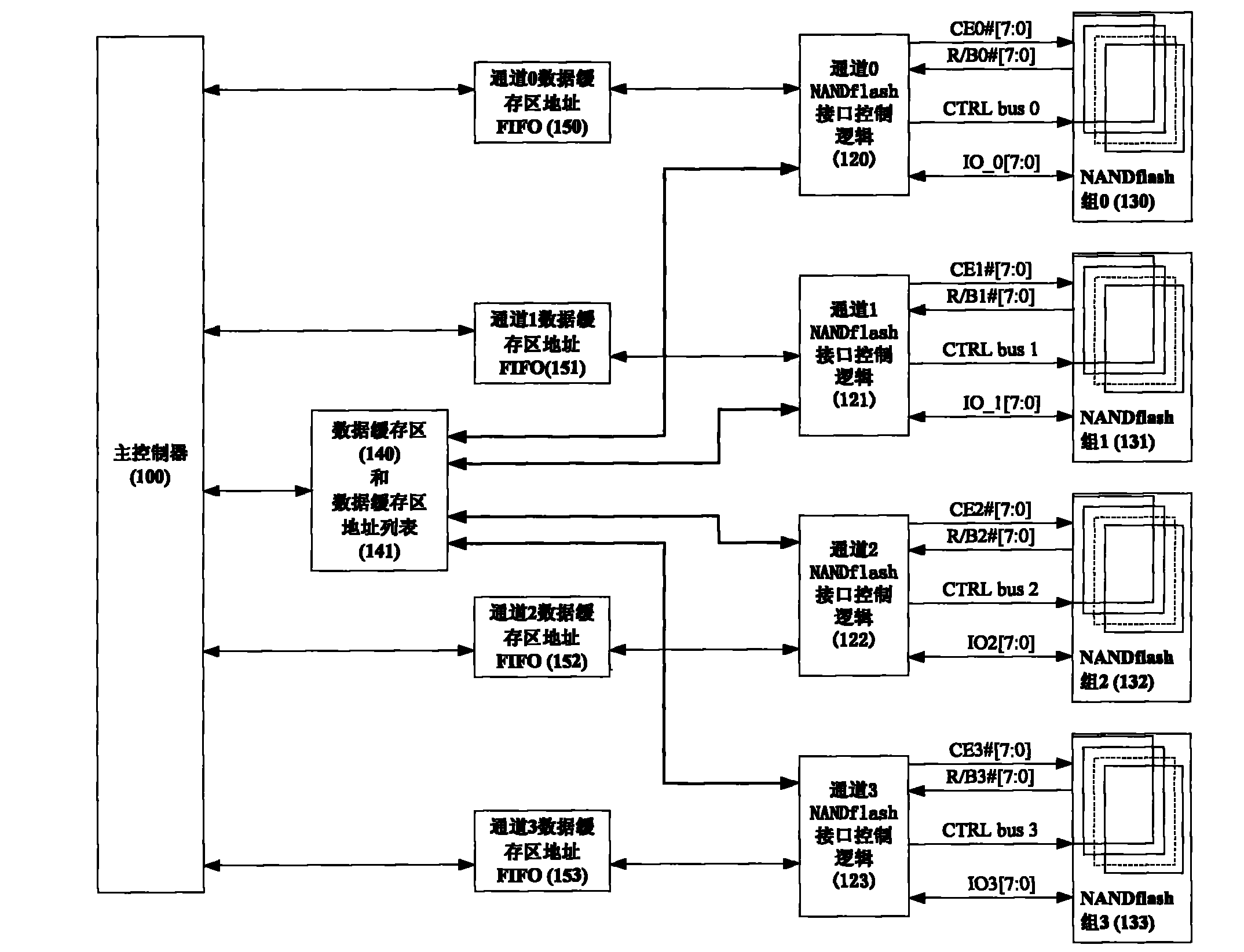

[0028] specific implementation plan

[0029] According to the solution provided by the present invention, select the best embodiment in conjunction with each accompanying drawing and describe the implementation of the content of the invention:

[0030] (1) The size of the single-channel buffer area when the data buffer area is exclusive

[0031] When each channel exclusively shares the data buffer area, the size of each channel's data buffer area is determined by the data storage strategy on the NAND flash. The storage strategy of data on NAND flash refers to how the system allocates data with continuous logical addresses to different NAND flashes. Data can be stored in blocks, pages, sectors or other sizes. exist on different NANDflash. The size of each channel data buffer is usually the size of a data unit. In the embodiment of the present invention, the data unit is a sector with a size of 512 bytes.

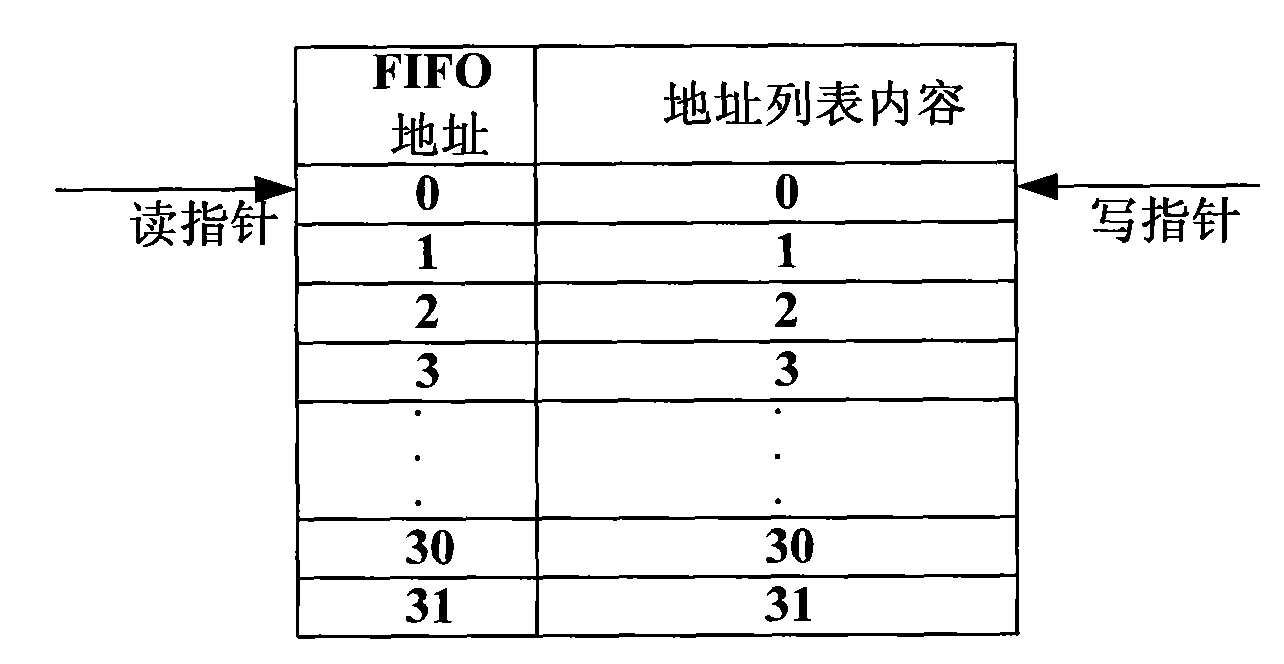

[0032] (2) Shared data buffer area, data buffer address list, buffer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com