Clock adjustment circuit and adjustment method for clock circuit

A clock adjustment and circuit adjustment technology, applied in the field of microelectronics, can solve the problems of increasing phase error, charge and discharge current mismatch, etc., to improve the speed of adjustment, improve accuracy, reduce phase error and control voltage ripple the effect of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

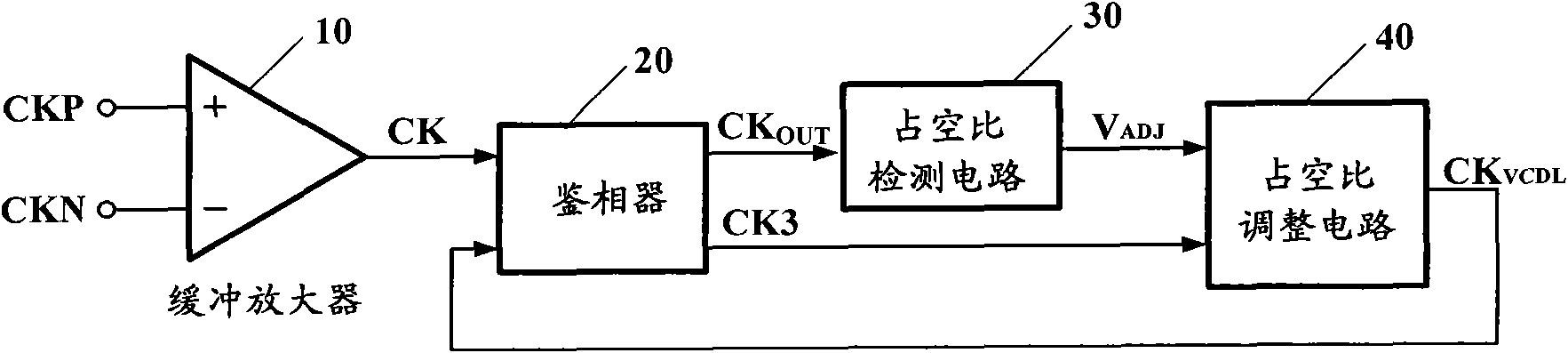

[0051] figure 1 is a structural block diagram of a clock adjustment circuit according to an embodiment of the present invention, such as figure 1 As shown, the duty cycle adjustment circuit includes:

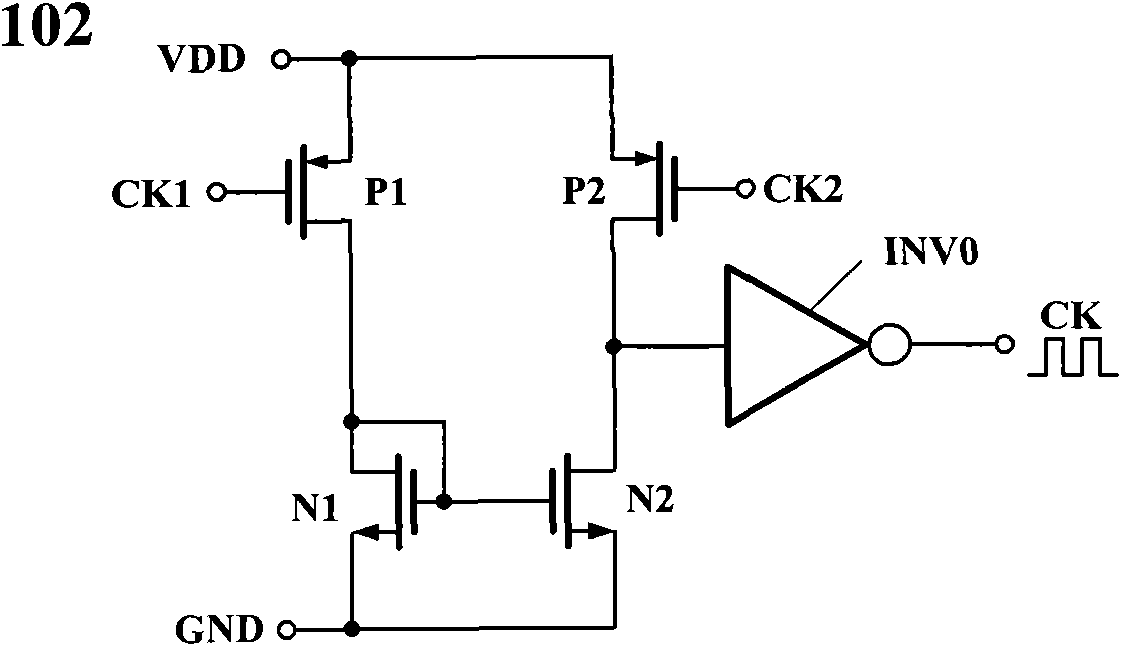

[0052] A clock buffer amplifier 10 is used to receive an external differential clock signal, reshape the differential clock signal into a single-ended square wave clock signal, and output the single-ended square wave clock signal;

[0053] The phase detector 20 is used to receive the single-ended square wave clock signal from the clock buffer amplifier and the feedback signal from the duty r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com