Transistor structure with reinforced total dose radiation resistance

A radiation-hardening, anti-total dose technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing the dynamic power consumption of the circuit, large gate area, reducing the circuit performance, etc., to reduce the channel width, Small aspect ratio, the effect of reducing parasitic leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

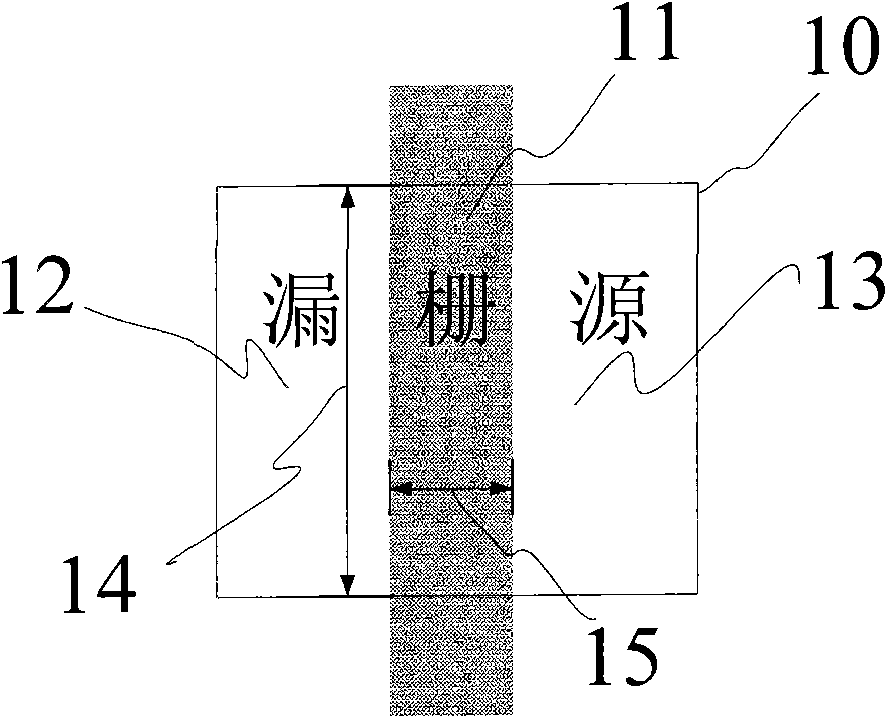

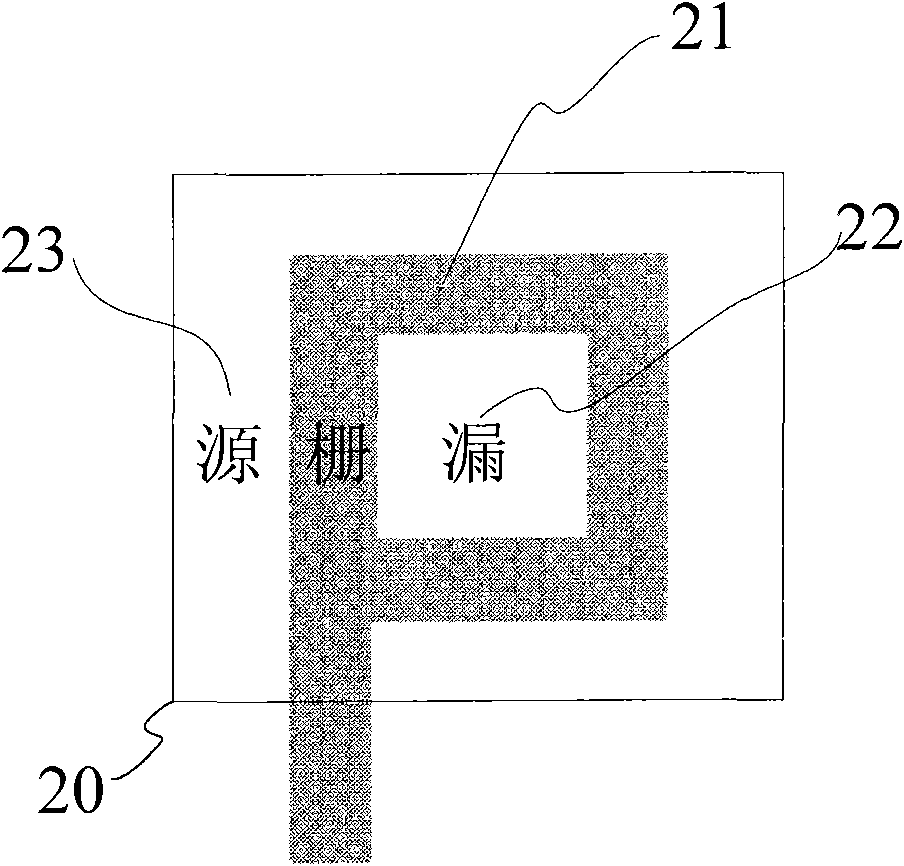

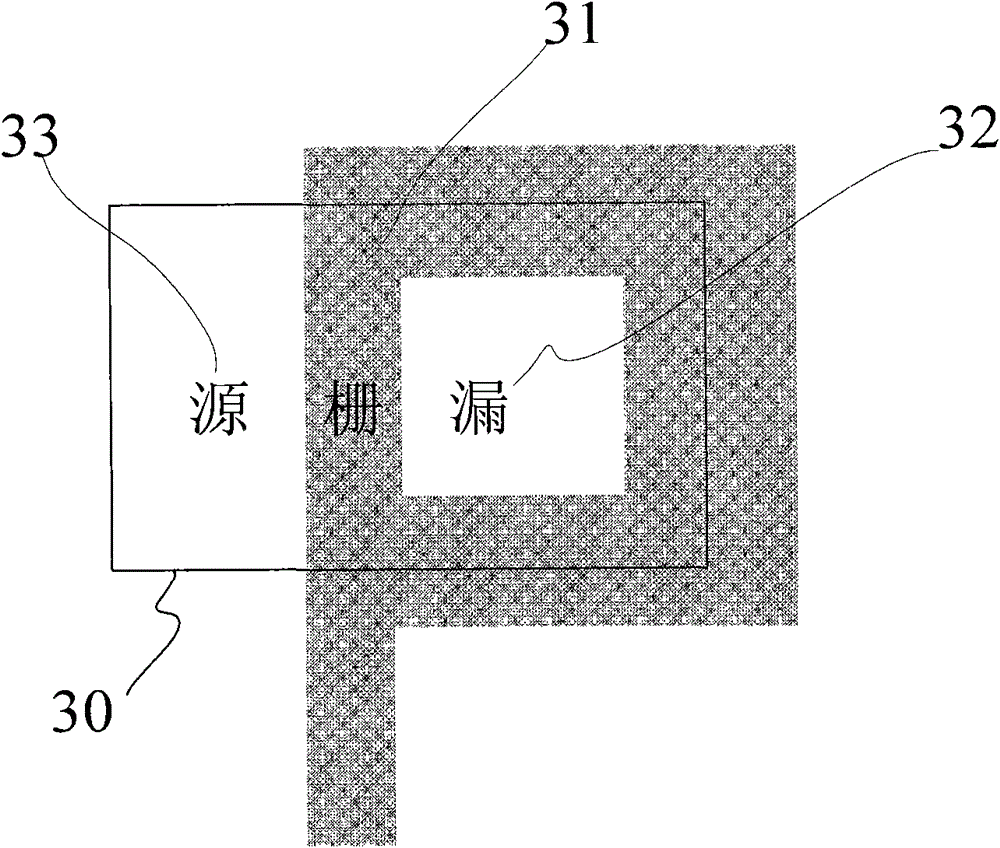

[0020] The anti-total dose radiation-hardened transistor structure of the present invention includes a gate region, a drain region, a source region and a floating region, and the gate region, the drain region, the source region and the floating region are all distributed in the same active region And the gate area separates the active area into a source area, a drain area, and a floating area. There is no intersecting area between the drain area, the source area, and the floating area. The drain area is completely surrounded by the gate area, and the source area is partially surrounded by the gate area. Surrounded or completely surrounded, the floating region is partially surrounded by the gate region; the floating region refers to the region that has the same doping type and the same doping concentration as the source region and the drain region and is not drawn out by wiring. In a transistor, there is one drain region, no less than one source region, and no less than one floa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com