Access control method of synchronous dynamic memory

A technology of synchronizing dynamics and control methods, applied in instruments, electrical digital data processing, etc., can solve the problems of high bus utilization, low efficiency, low effective bus utilization, etc., to improve bus efficiency, efficient data interaction, and save Bank. The effect of changing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

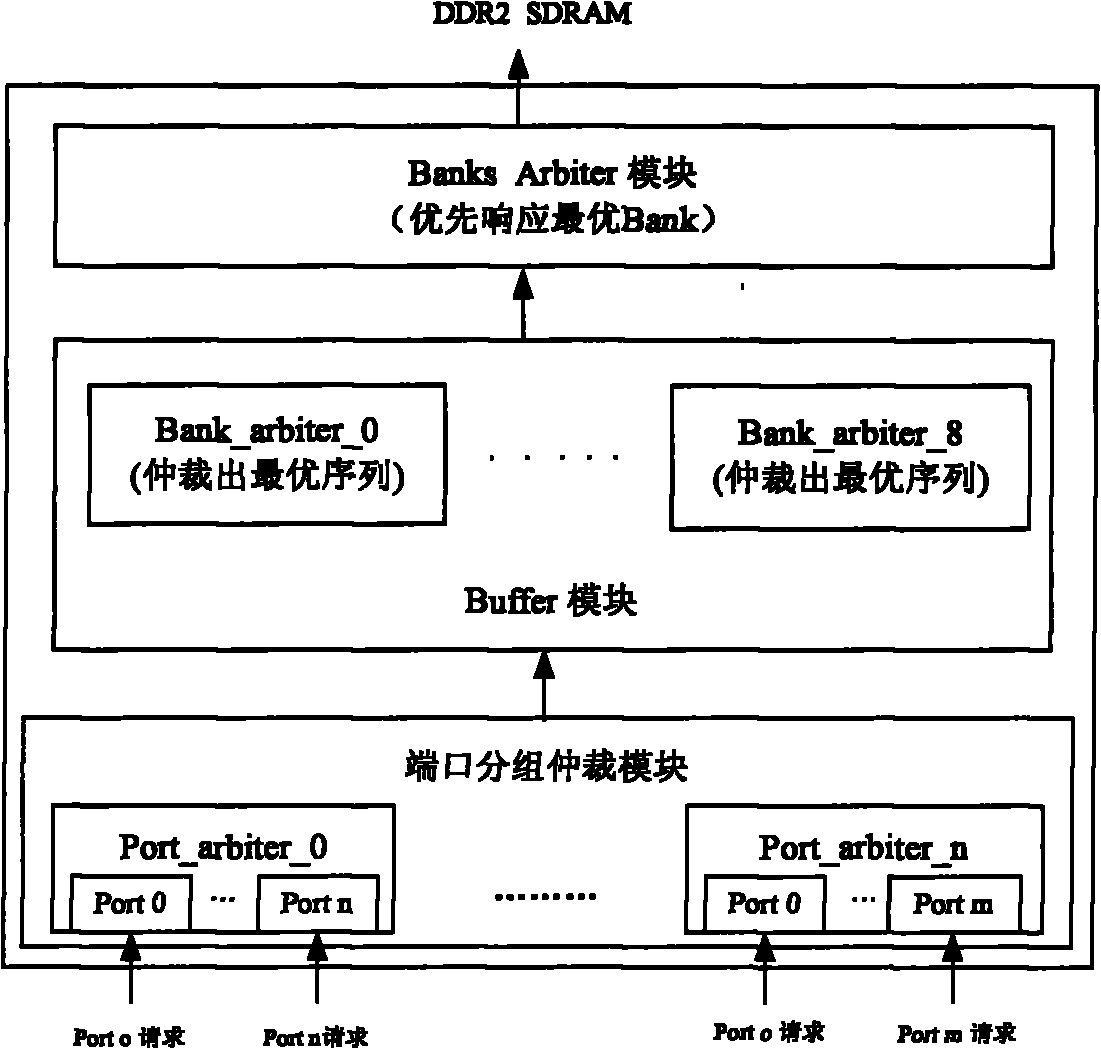

[0019] This embodiment adopts a scheduling mechanism that combines port group arbitration, internal bank arbitration, inter-bank arbitration, Round robin algorithm, out-of-order scheduling algorithm, and weighted coefficient arbitration algorithm. Its scheduling structure is as follows image 3 As shown, the scheduling structure of the synchronous dynamic memory controller includes three parts: 1) port group arbitration module; 2) Buffer module; 3) Banks Arbiter module.

[0020] 1) The port group arbitration module adopts a port group arbitration mechanism: all ports requesting data from the memory are divided into several groups according to their own characteristics, and each port group is configured with a sub-arbitrator. Each sub-arbitrator first uses the traditional Roundrobin scheduling algorithm to arbitrate each port request to obtain a reasonable sequence. At the same time, according to the characteristics of each request port, calculate the proportion of the bus ban...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com