ESD protective device

An ESD protection and protection device technology, applied in emergency protection circuit devices, circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc., can solve problems such as poor conduction uniformity, and achieve higher gate voltage. , The effect of reducing the on-voltage and improving the ESD protection capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

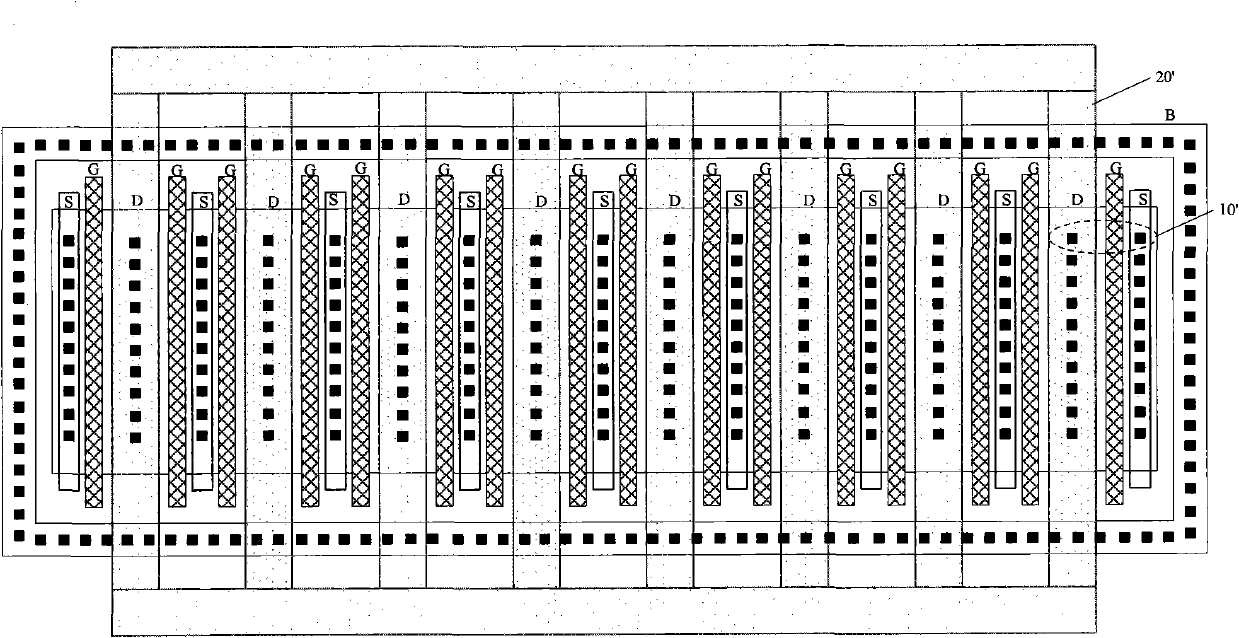

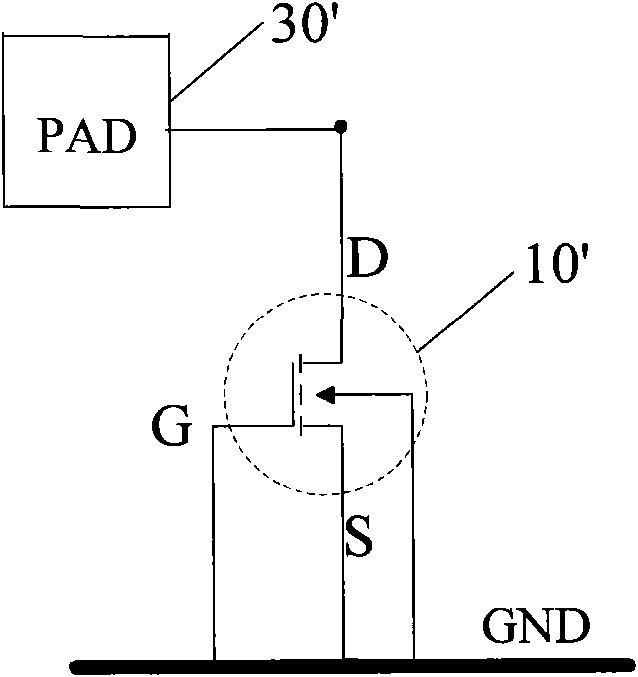

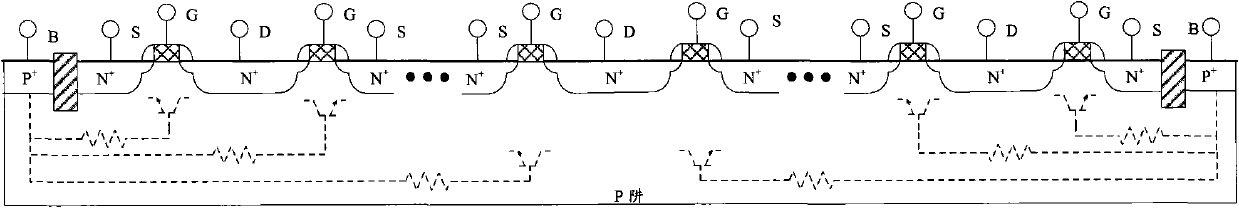

[0032] The ESD protection device provided by this embodiment is as Figure 5 As shown, the device is a multi-finger NMOS protection device located in a P well, and the device includes: a plurality of enhanced NMOS transistors 10 and a multi-finger metal layer 20 .

[0033] The plurality of enhanced NMOS transistors 10 are arranged in a matrix, and the cross-sections of the NMOS transistors 10 in each row are shown in Image 6 ; The source S and grid G of the NMOS transistor 10 are grounded (see Figure 7 ); the base of each parasitic NPN transistor of the NMOS transistor 10 is grounded through the parasitic base resistance in the P well. In this embodiment, the base of the parasitic NPN transistor is grounded through the base resistor, specifically, the B that is in contact with the P well is grounded; the black square is a tungsten plug.

[0034] The metal layer 20 covers the drains D of each row of the NMOS transistors 10 and overlaps the gates G of two columns adjacent ...

no. 2 example

[0039] This embodiment provides an ESD protection device (see Figure 5 ), the device is a multi-finger PMOS protection device located in an N well, and the device includes a plurality of enhanced PMOS transistors and a multi-finger metal layer.

[0040] The multiple enhanced PMOS transistors are arranged in a matrix; the source and gate of the PMOS transistors are grounded; the base of each parasitic PNP transistor of the PMOS transistors is grounded through the parasitic base resistance in the N well.

[0041] The metal layer covers the drains of each row of the PMOS transistors and overlaps with the two rows of gates adjacent to the drains, the metal layer is connected to the PAD and connected to the drains; the metal layer is connected to the drains The overlapping gates form parasitic capacitance.

[0042] When a negative ESD pulse occurs on the PAD, the parasitic capacitance couples the gate voltage to a negative potential, increases the leakage current from the drain t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com