Masking method for deep-etching multi-layer silicon structure by dry method

A silicon structure, multi-layer silicon technology, applied in microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve problems such as poor dimensional accuracy, structural sidewall and edge deformation, and achieve perfect edge structure and dimensional accuracy. High, process repeatability effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

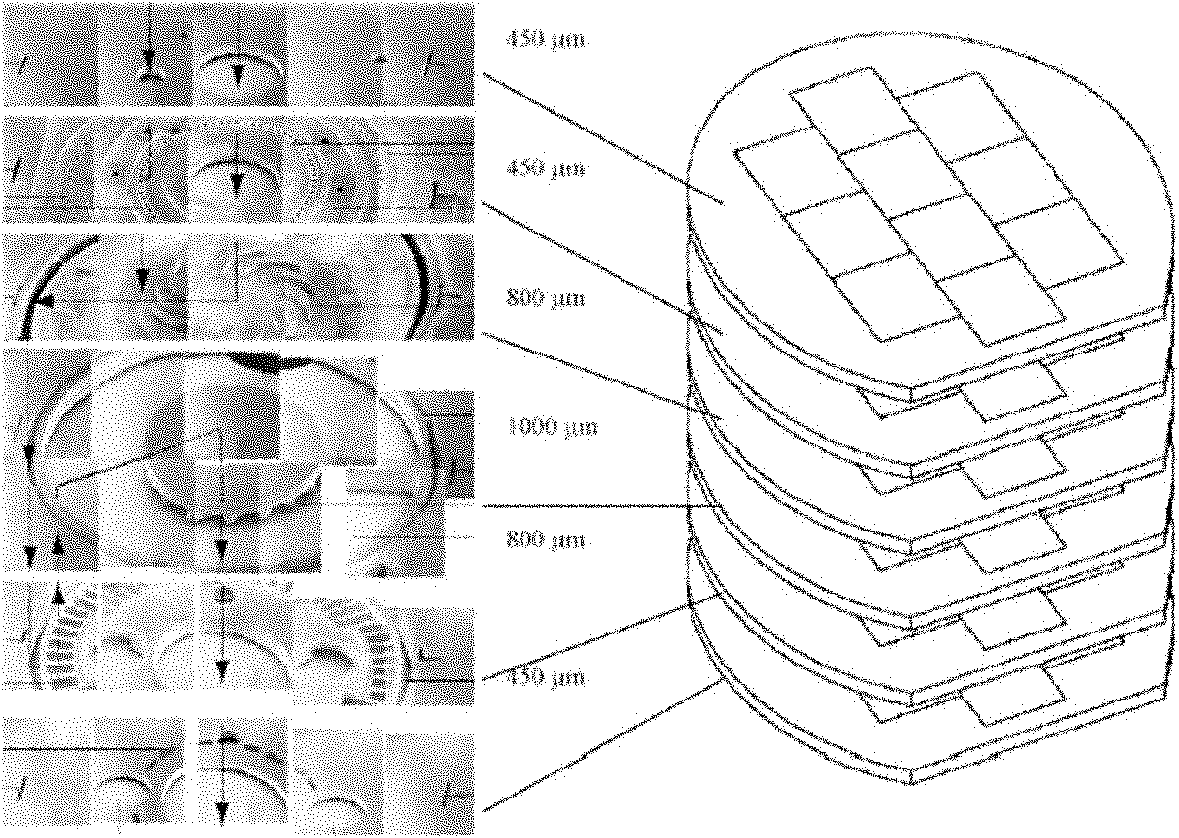

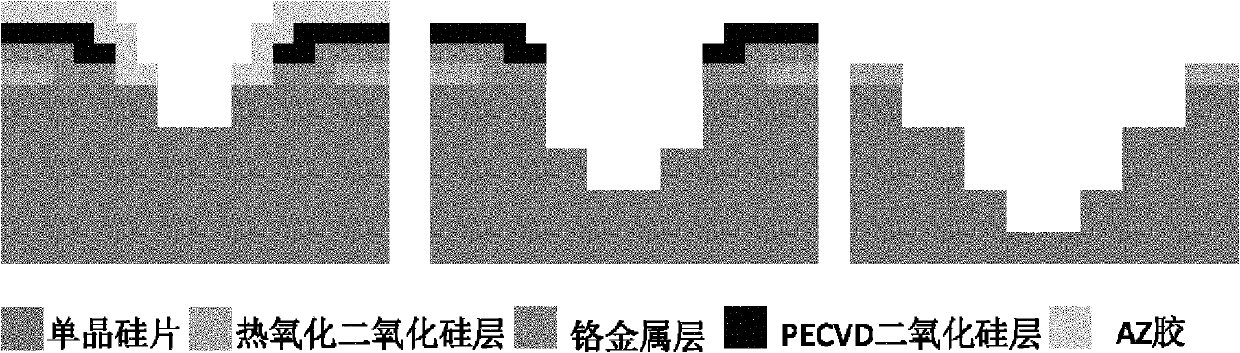

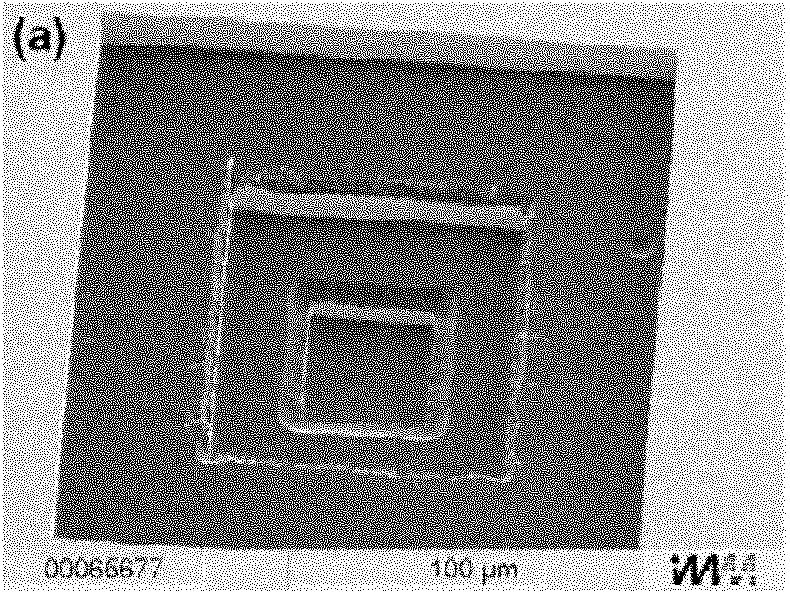

[0063] FIG. 7 is a process flow chart of specific steps 1 to 13 of a novel multilayer silicon dry deep etching mask.

[0064] In the figure: 7a to 7m represent steps 1 to 13 respectively.

[0065] Step 1: Select a suitable monocrystalline silicon wafer (4 inches, 400um thick, )

[0066] a) RCA2 wash-DI:H 2 o 2 : HCL=10:2:1; 50°C, 15-20mins.

[0067] b) Wafer container: Teflon cassette

[0068] c) Equipment: fume hood

[0069] Step 2: Apply Az4620P photoresist

[0070] a) 15s, 600rpm; 25s, 3000rpm. (7.3um thickness)

[0071] b) Equipment: Spin coater KW-4A homogenizer

[0072] Step 3: UV lithography to obtain the first layer mask

[0073] a) 1.7mw / cm 2 x 60s=102mJ / cm 2

[0074] b) Equipment: Karl Suss MA4, 400nm

[0075] Step 4: DRIE etching the first layer structure

[0076] a) Process conditions: Table 2, 40 cycles

[0077] b) Equipment: Oxford PlasmaLab 100etcher

[0078] c) Depth of etching structure: 50um

[0079] Step 5: Clean the residual Az photoresist m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com