ESD protection integrated power MOSFET or IGBT and preparation method thereof

An ESD protection and power technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as complex circuits, increased manufacturing costs, and large area occupied by ESD protection, achieving good universality, The effect of cost reduction and improvement of ESD discharge capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

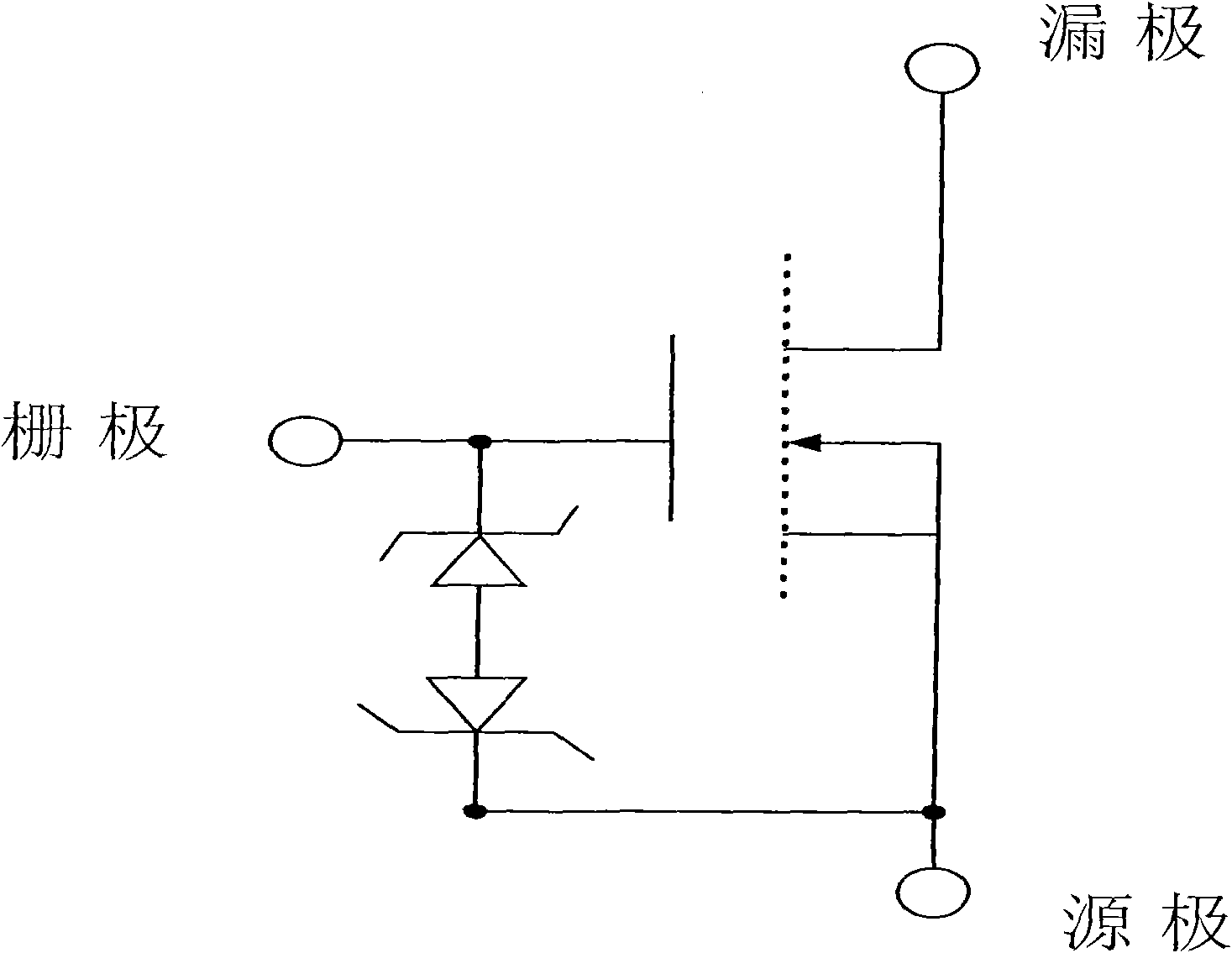

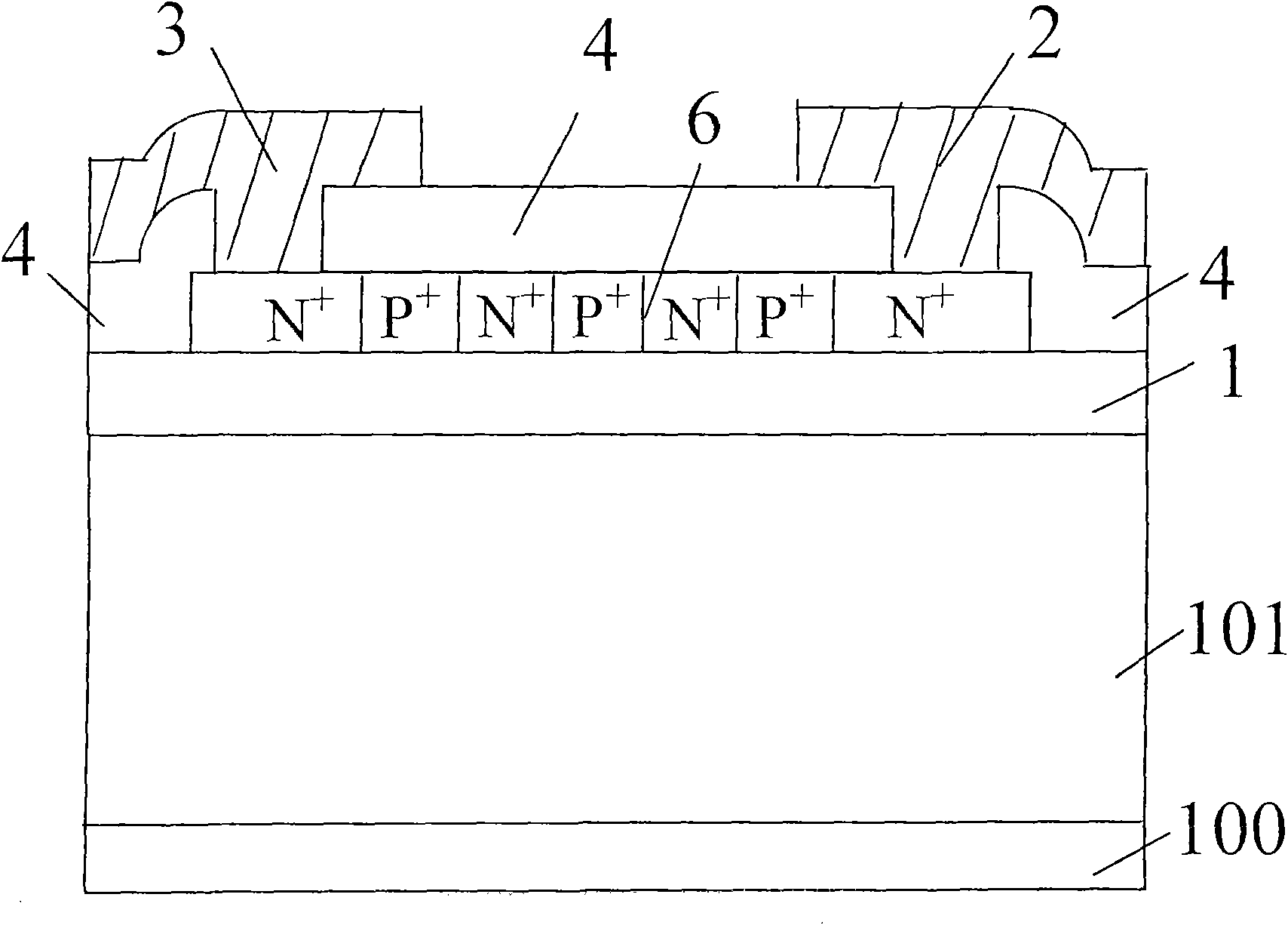

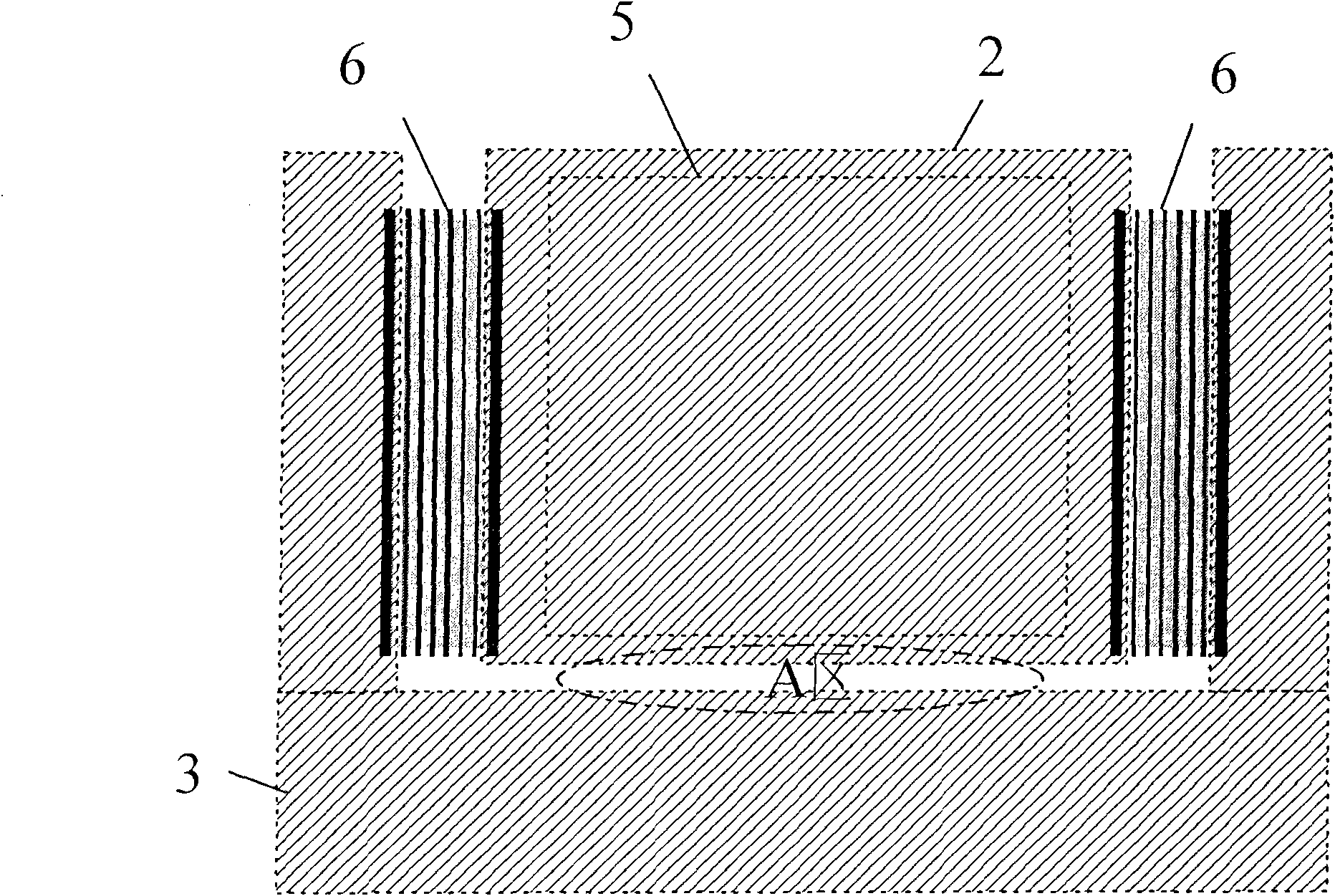

[0037] Embodiment 1: see attached Figure 5 , 9 , the ESD protection unit of the present invention integrated ESD protection power MOSFET, from bottom to top: substrate 100, epitaxial layer 101, oxide layer 1, polysilicon diode group 7, dielectric layer 4, gate metal 2 and source metal 3 . Gate metal 2 and N at one end of polysilicon diode group 7 + The doped region is connected to the gate of the power MOSFET, the source metal 3 is connected to the other end N of the polysilicon diode group 7 + Doped region and power MOSFET source connection. There may be a passivation layer (not shown in the figure) on the gate metal 2 and the original metal 3 . The ESD protection unit is disposed on the gate bonding area of the power MOSFET and half surrounds the gate bonding area 5 between the cells.

[0038] Preparation: According to the usual power MOSFET preparation process, for example: use 920°C wet oxygen oxidation to grow about 500A pre-oxidation, and then perform photolithog...

Embodiment 2

[0039] Embodiment 2: as embodiment 1, wherein the power MOSFET source N + The advancing temperature was changed from 950°C to 970°C, and the time was changed from 150 minutes to 180 minutes, which reduced the gate-source breakdown voltage.

Embodiment 3

[0040] Embodiment 3: see Image 6 , as in Embodiment 1 or 2, wherein the P at one end of the polycrystalline diode group 7 + The doped region is connected to the gate of the power MOSFET, the source metal 3 is connected to the other end P of the polysilicon diode group 7 + Doped region and power MOSFET source connection. The two ends of the polycrystalline diode group of the ESD protection unit are P-type regions, and the P-type regions at both ends are composed of P - / P + structure composition, and P + At the outermost end of the diode group, the remaining P regions of the polycrystalline diode group are connected to the P - / P + P in the structure - the same, N + The dose to the zone is 5E15cm -2 -1.5E16cm -2 , P + The dose is 5E14cm -2 -8E15cm -2 . P + The advance time is 90 minutes.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com