TFT (Thin Film Transistor) array structure and manufacturing method thereof

A technology of array structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., to reduce difficulty and cost, solve crosstalk and distortion, and improve yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

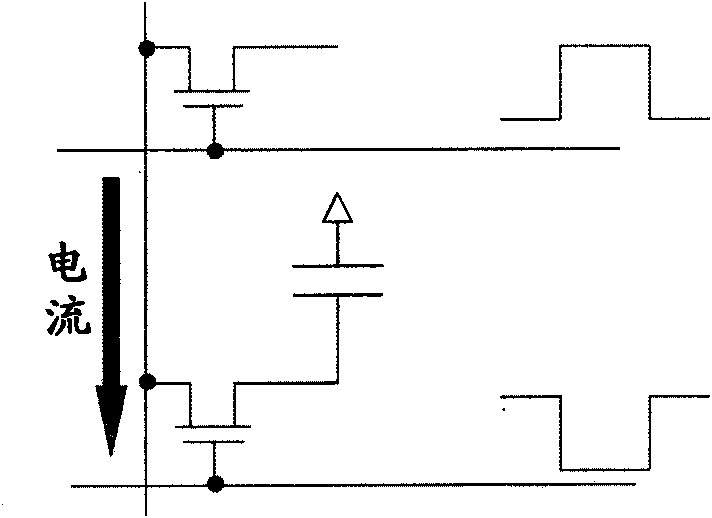

[0048] In-plane switching liquid crystal display (IPS-LCD) is one of the mainstream wide viewing angle LCD technologies. The difference from twisted array liquid crystal display (TN-LCD) is that the common electrode and pixel electrode of IPS-LCD are fabricated on the substrate. On the same side, the common electrode and the pixel electrode are driven by the horizontal driving electric field, which can make the liquid crystal molecules rotate on the plane and greatly increase the viewing angle.

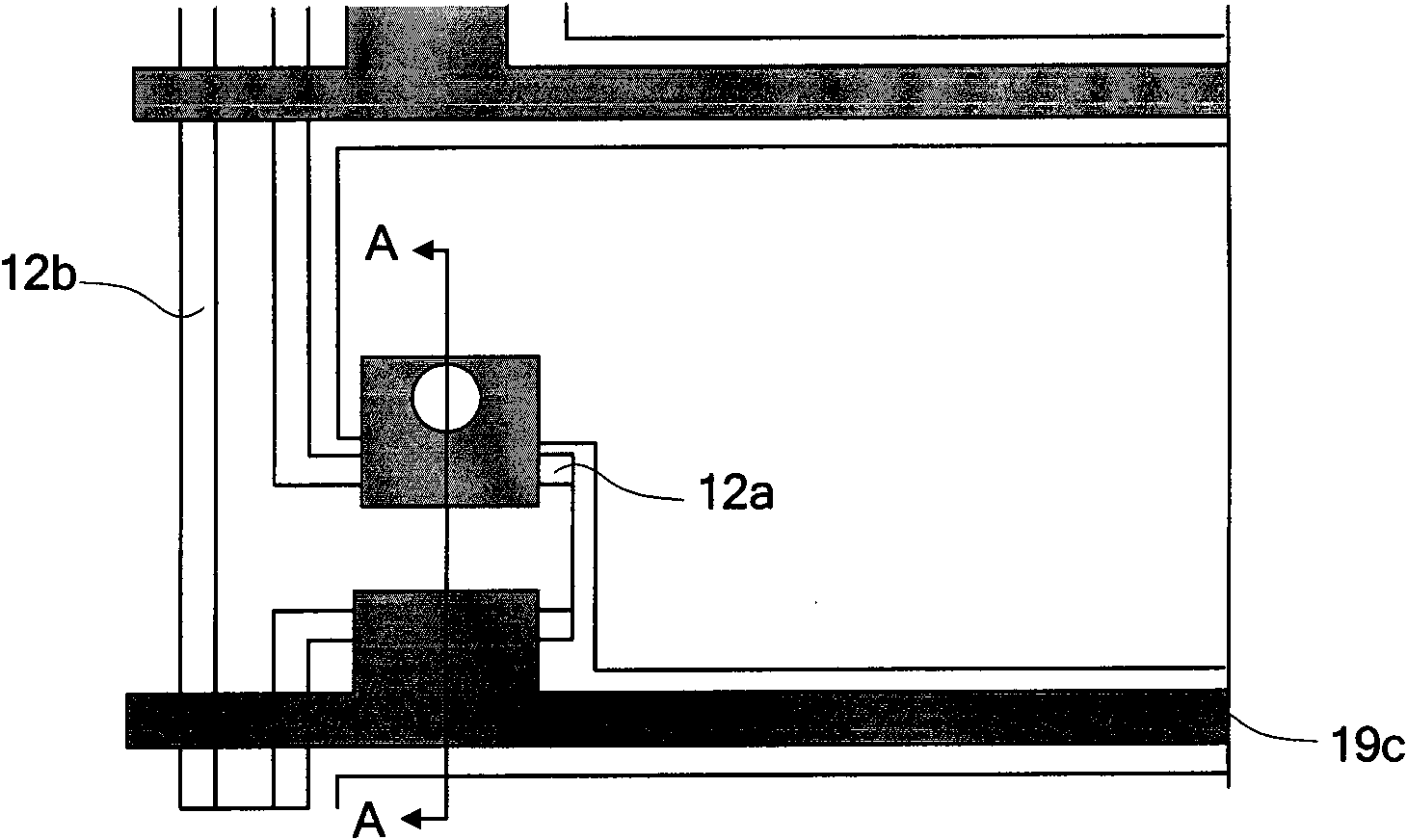

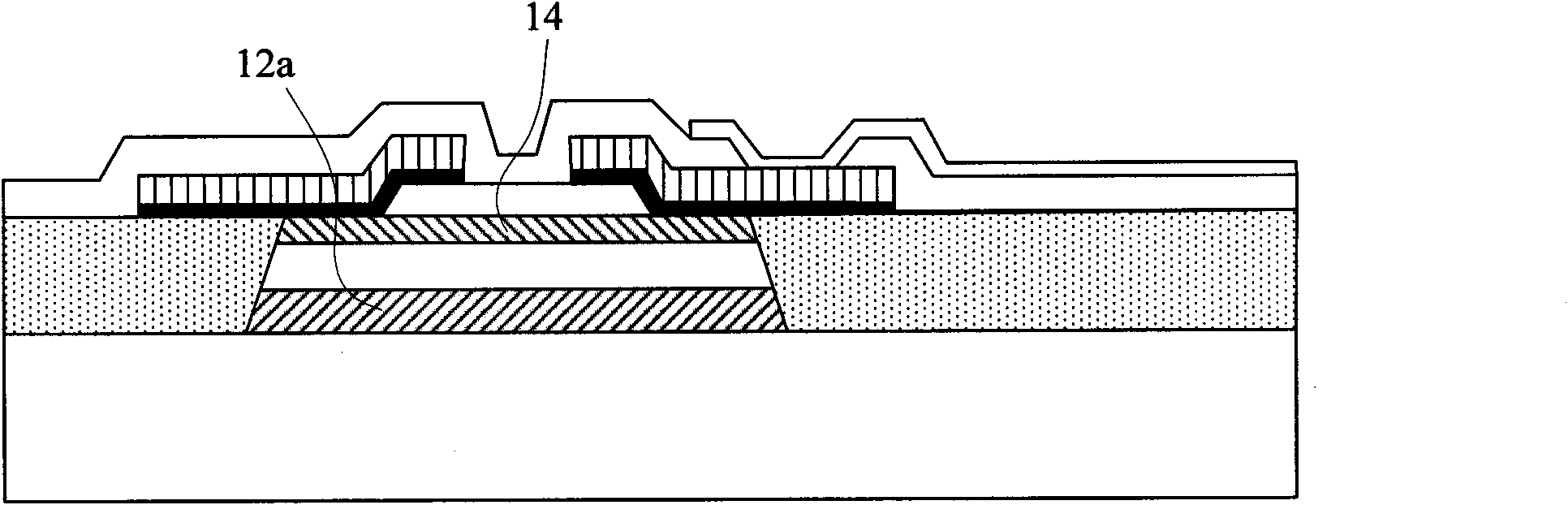

[0049] Please refer to Figure 4 to Figure 5 ,in, Figure 4 It is a top view of the TFT array structure proposed in the first embodiment of the present invention, Figure 5 for Figure 4 Sectional view of part A-A in middle, Figure 6 for Figure 4 Sectional view of part B-B in middle.

[0050] As shown in the figure, the TFT array structure 200 that can be used for IPS-LCD includes: a substrate 210, a gate line 224 and a common electrode 222 formed on the substrate 210, a data l...

no. 2 example

[0073] Please refer to Figure 8 to Figure 10 ,in, Figure 8 It is a top view of the TFT array structure proposed in the second embodiment of the present invention, Figure 9 for Figure 8 Sectional view of part A-A in middle, Figure 10 for Figure 8 Sectional view of part B-B in middle.

[0074]As shown in the figure, the TFT array structure 300 that can be used for TN-LCD includes: a substrate 310, a gate line 324 and a common electrode 322 formed on the substrate 310, a data line 383 intersecting with the gate line 324; The common electrode 322 and the insulating layer 361 on the substrate 310; the TFT formed at the intersection of the gate line 324 and the data line 383, wherein the TFT includes a gate 323 integrated with the gate line 324, which is sequentially formed on the The gate insulating layer 331 and the semiconductor layer 341 on the gate 323, the drain 381 and the source 382 integrated with the data line 383; wherein, the gate between two data lines 383 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com