Automatic Verilog HDL code generator of parallel CRC (Cyclic Redundancy Check) algorithm and method thereof

A CRC algorithm and automatic generation technology, applied in the direction of program control devices, etc., can solve the complex problems of VerilogHDL code generation, and achieve the effect of rapid generation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

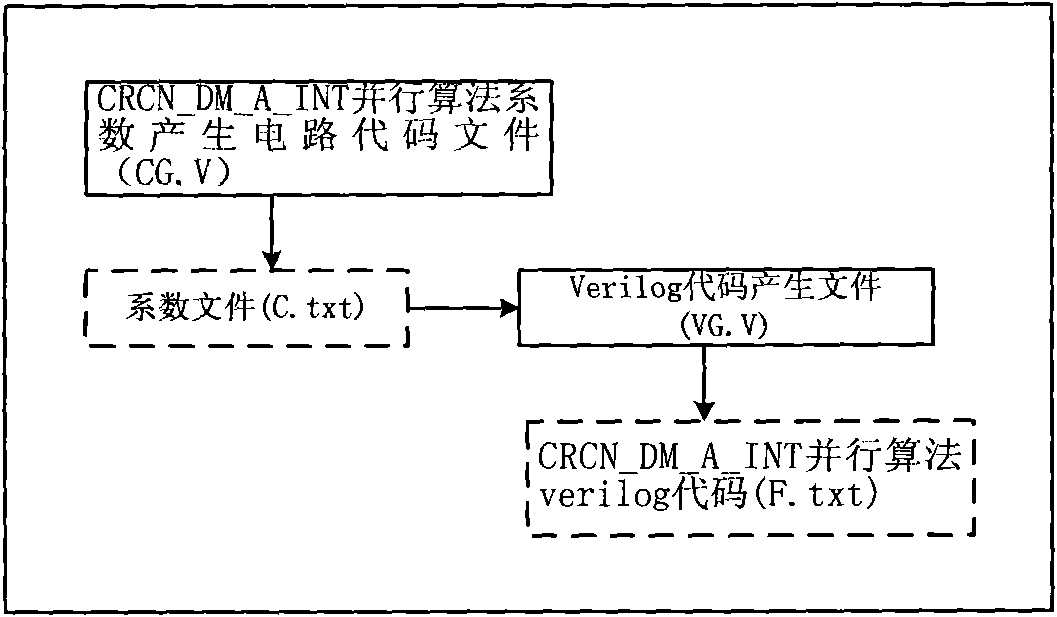

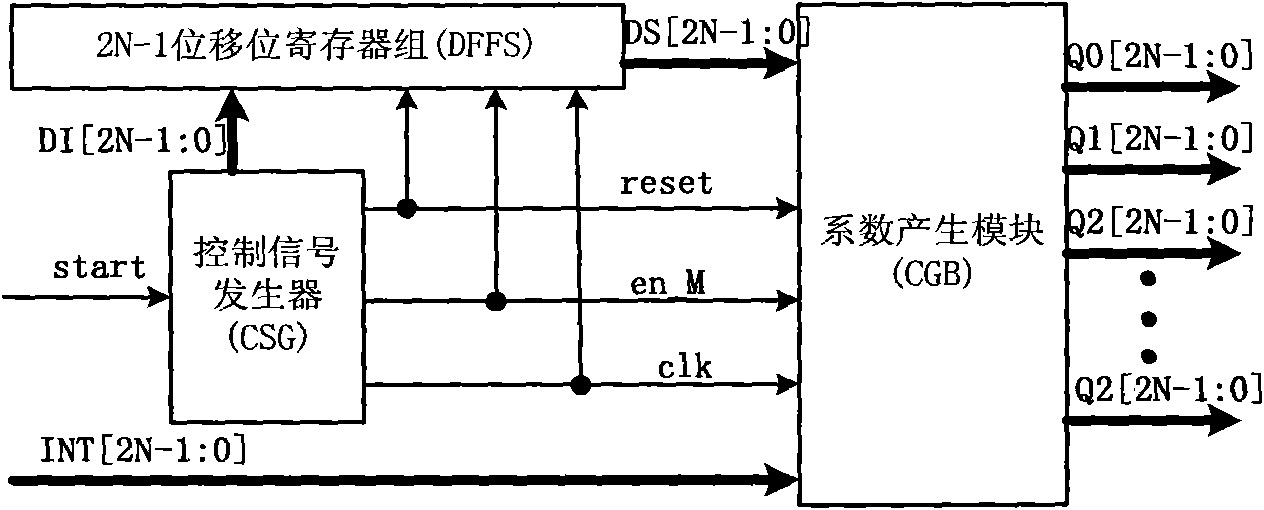

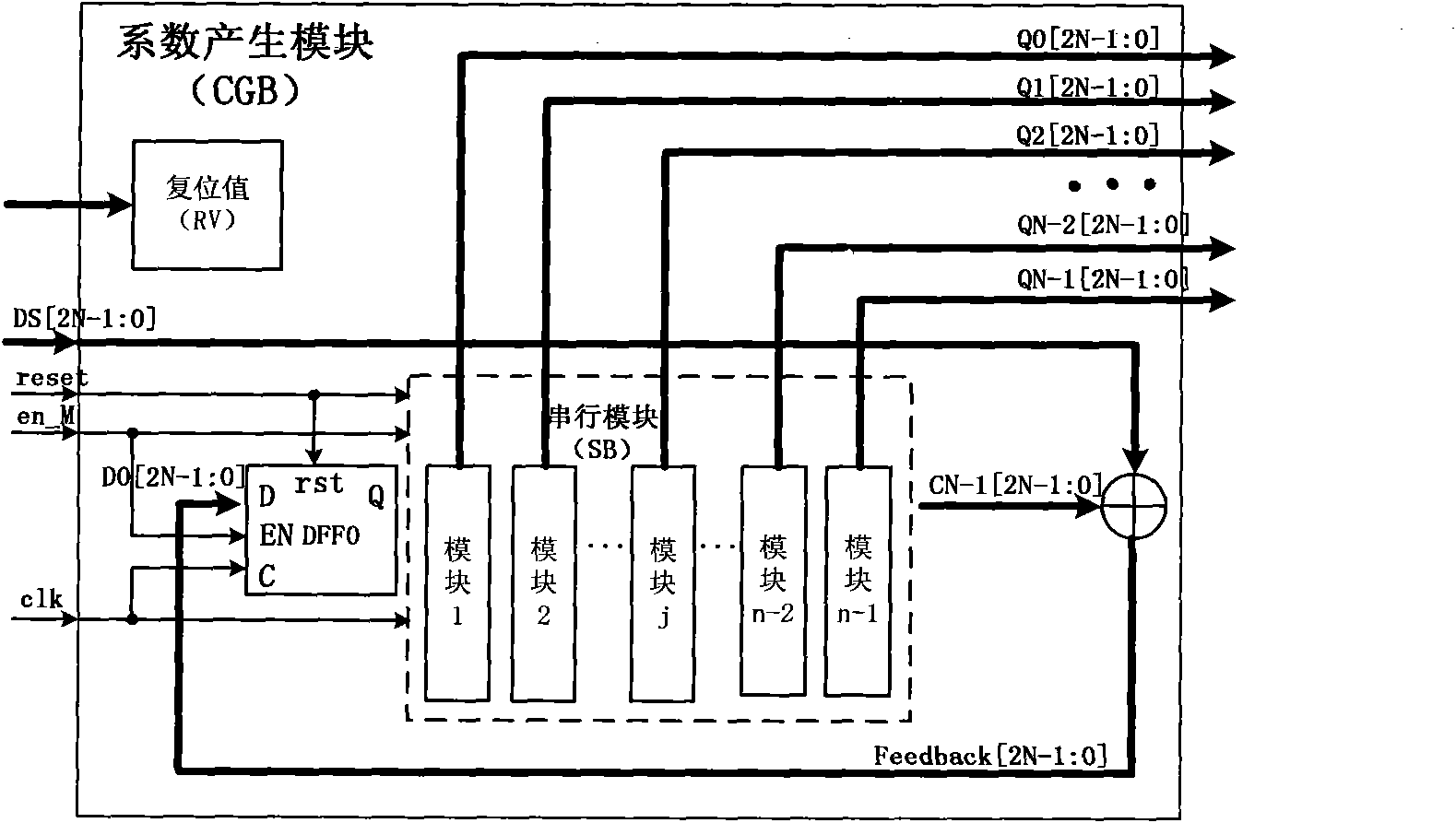

[0053] The present invention converts the serial CRC circuit into a parallel CRC circuit, that is, obtains the parallel CRC circuit according to the structure or expression (formula 1) of the serial CRC circuit. The parallel CRC circuit can be represented by Verilog code (F.txt); its general form is represented by formula 2, and the specific code will be generated in the file F.txt;

[0054]The core problem in formula 2 is the coefficient Qj[i] of each item, and the specific coefficient will be generated in the file C.txt;

[0055] The file C.txt can be generated by running CG.v in modelsim;

[0056] CG.v is the verilogHDL code representation method of the parallel CRC coefficient generation circuit CRCN_DM_A_INT; the CRC coefficient generation circuit is the core of this patent protection, and its design method is given by the coefficient generation circuit design steps (Appendix 3);

[0057] The parameters to be used in the design step are N, M, A, INT

[0058] The paramet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com