Link layer controller of IEEE1394 bus

A technology of link layer and controller, which is applied in the direction of bus network, data exchange through path configuration, electrical components, etc. It can solve the problems that aerospace-grade devices are not easy to obtain, and achieve good versatility and high performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be described in detail below with reference to the drawings.

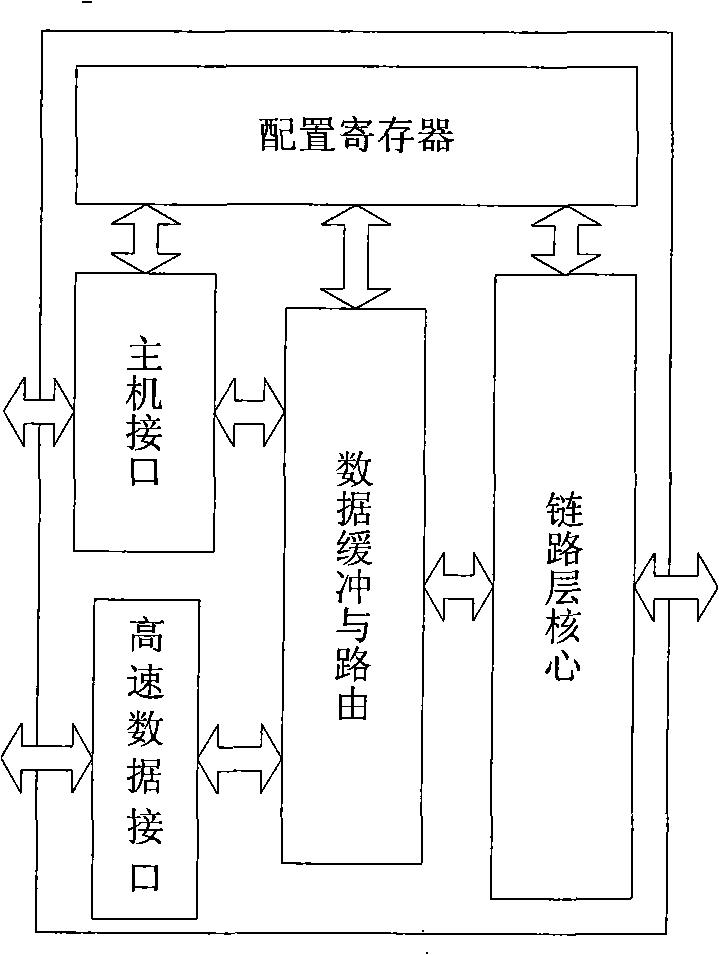

[0041] Such as figure 1 As shown, the present invention is composed of five basic modules: host interface, high-speed data interface, data buffer and routing, link layer core module and configuration register.

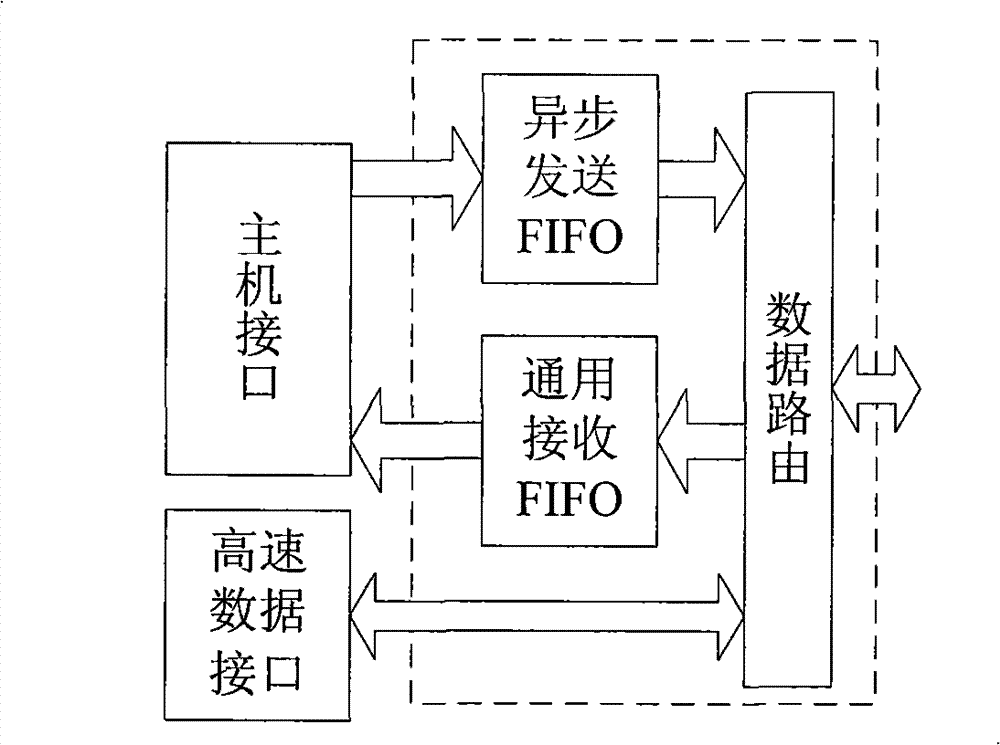

[0042] The host interface part provides a universal 16-bit CPU interface, through which timing coordination with different CPUs can be realized. The host interface module is internally connected to the configuration register, data buffer and routing control module through a 16-bit bidirectional data bus and some control lines. The external CPU can use this interface to read and write the configuration register inside the link layer controller, and access the data buffer: write the data packet to be sent or read the received data packet. The timing of the host interface is completed under the control of the clock signal provided by the external CPU. Therefore, the read and write...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com