High-speed shadow memory control structure

A memory controller and control structure technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve problems such as bus conflicts, affecting data transmission speed, etc., achieve overall performance improvement, improve data access speed and read accuracy , the effect of reducing the difficulty of development

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Embodiments of the present invention are described in further detail below in conjunction with the accompanying drawings:

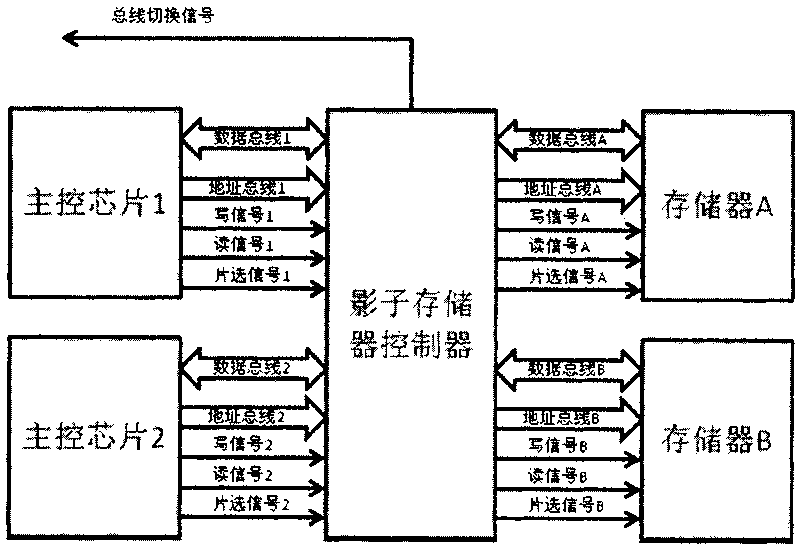

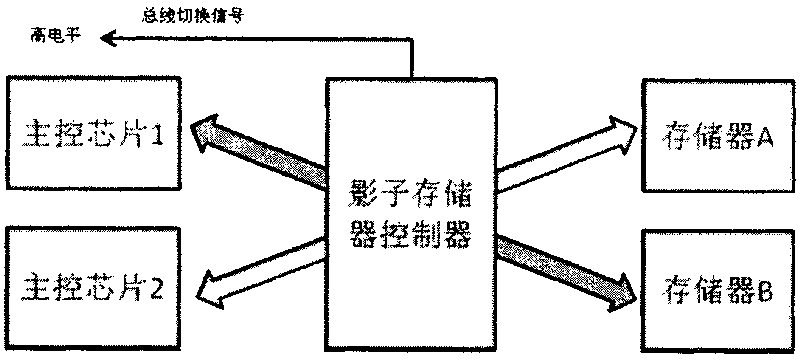

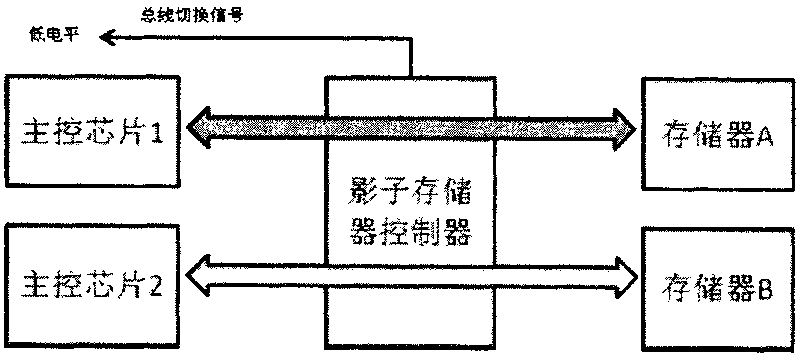

[0019] A high-speed shadow memory control structure, such as figure 1 As shown, it consists of two main control chips, a shadow memory controller, and two memories that are shadows of each other. The two memories are respectively connected to the shadow memory controller through two sets of data buses, address buses and control signals, and the shadow memory controller is also connected to the two main control chips through another two sets of address data buses, address buses and control signals. The control signals include read signal, write signal and chip select signal. The bus switching signal of the shadow memory controller is connected to any control module. The bus switching signal of the shadow memory controller can also be connected to other logic switching chips. In this control structure, the main control chip can use single-chip micro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com