Preparation technique of gradient diffusion impervious layer used for deep submicron integrated circuit Cu interconnection

A gradient diffusion, deep submicron technology, applied in the manufacture of circuits, electrical components, semiconductor/solid devices, etc., can solve the problems of high process complexity, thermal stability damage of heterogeneous buffer layer, and solid solution α-Ta resistivity High-level problems, to achieve the effect of mature technology, reduce the adsorption of pollution elements, improve the bonding strength and adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] The present invention adopts self-developed radio frequency reactive magnetron sputtering coating equipment;

[0033] The purity of the sputtering metal Ta target used is 99.99%; the working gases Ar and N 2 The purity is 99.999%;

[0034] The deposition thickness of the double-layer gradient diffusion barrier layer is 100nm;

[0035] The entire deposition process is carried out at room temperature, and this embodiment is a double-layer gradient diffusion barrier layer prepared with optimal process parameters.

[0036] Under the above conditions, the preparation steps of the Ta / TaN gradient diffusion barrier layer are as follows:

[0037] (1) Treatment of the substrate before deposition

[0038] Put the single crystal Si(111) into acetone for ultrasonic cleaning for 20 minutes, then put it into absolute ethanol for ultrasonic cleaning for 20 minutes, after drying, put it into the vacuum chamber of the radio frequency reaction magnetron sputtering coating equipment, a...

Embodiment 2

[0047] The operation steps of this embodiment, the coating equipment used and other working conditions are all the same as in Example 1, and the total thickness of the double-layer gradient diffusion barrier layer deposition is kept constant at 100nm, and the amorphous TaN layer, TaN gradient layer, and metal TaN layer are adjusted. The deposition time of the layer is changed to change the thickness of each layer of the amorphous TaN layer, the TaN gradient layer and the metal Ta layer in the double-layer gradient diffusion barrier layer.

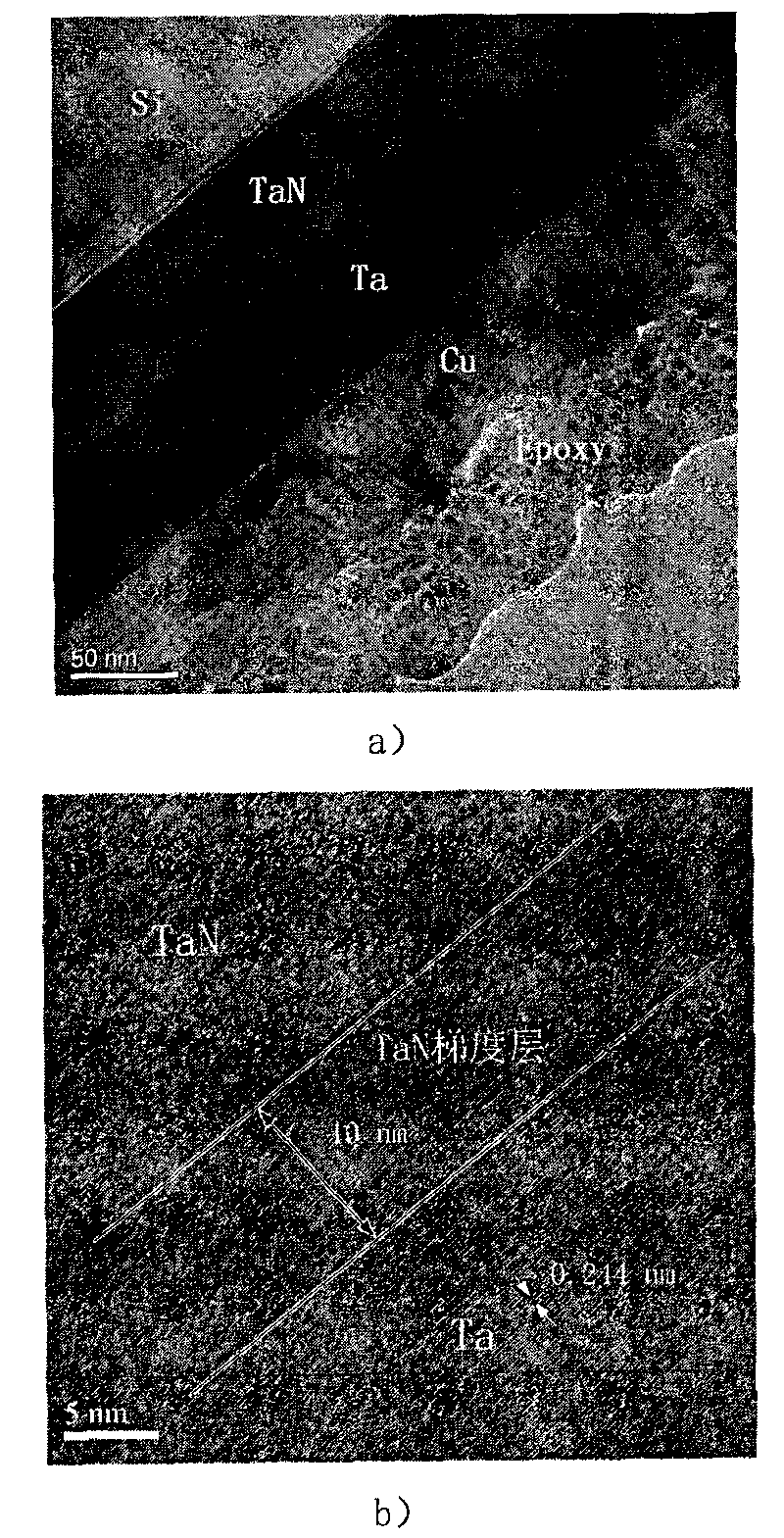

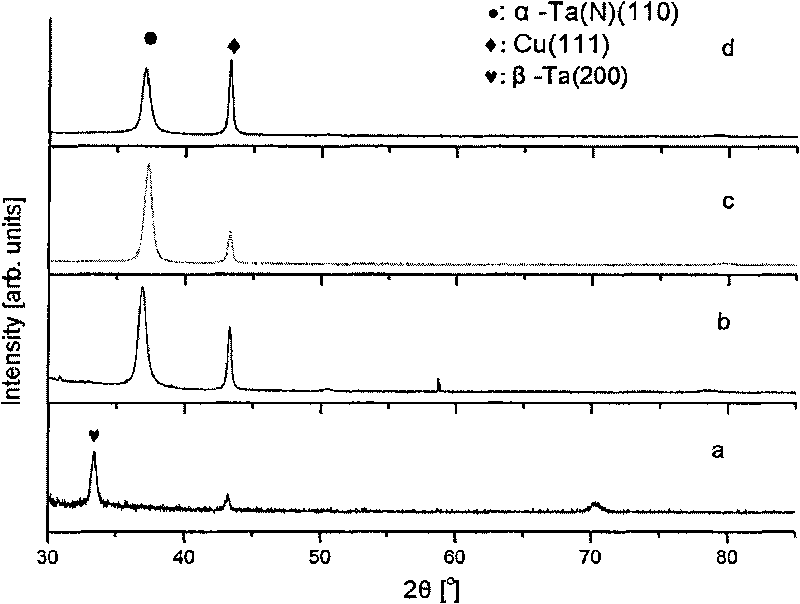

[0048] In this example, the deposition time of the amorphous TaN layer is 3min 50s, and the deposition thickness is 40nm; the deposition time of the TaN gradient layer is 1min, and the deposition thickness is 20nm; the deposition time of the Ta layer is 2min50s, and the deposition thickness is 40nm. / TaN gradient diffusion barrier samples. The obtained samples were analyzed by XRD, and all showed that the generated α-Ta was N solid solution...

Embodiment 3

[0050] The operation steps of this embodiment, the coating equipment used and other working conditions are all the same as in Example 1, and the total thickness of the double-layer gradient diffusion barrier layer deposition is kept constant at 100nm, and the amorphous TaN layer, TaN gradient layer, and metal TaN layer are adjusted. The deposition time of the layer is changed to change the thickness of each layer of the amorphous TaN layer, the TaN gradient layer and the metal Ta layer in the double-layer gradient diffusion barrier layer.

[0051] In this example, the deposition time of the amorphous TaN layer is 3min, and the deposition thickness is 35nm; the deposition time of the TaN gradient layer is 2min20s, and the deposition thickness is 30nm; the deposition time of the Ta layer is 2min20s, and the deposition thickness is 35nm. TaN gradient diffusion barrier layer samples, the obtained samples were analyzed by XRD, all showed that the generated α-Ta was N solid solution,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Deposition thickness | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com