Filling method of deep groove isolation structure of silicon-on-insulator

A silicon-on-insulator and isolation structure technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of etching gas concentration distribution edge effect, difficulty in controlling the thickness of amorphous silicon, and difficulty in controlling the thickness of oxide layer, etc. , to achieve the effect of avoiding polysilicon void phenomenon, good compactness and high yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

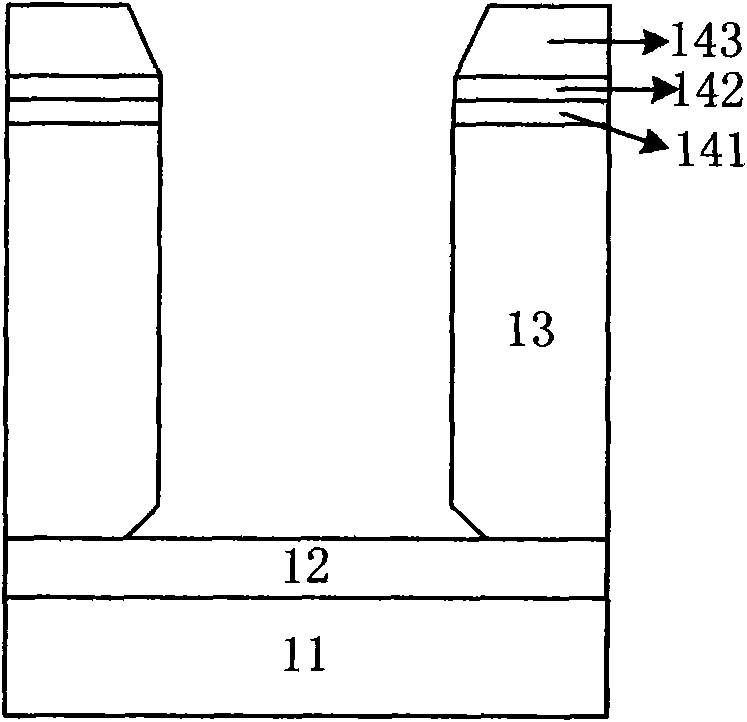

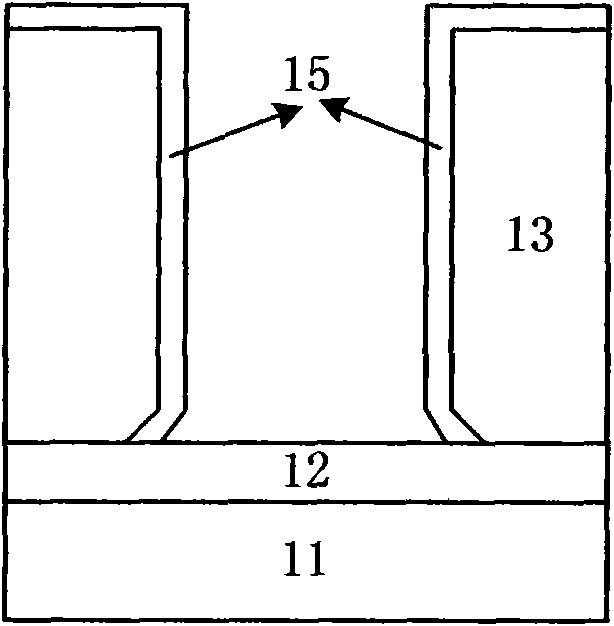

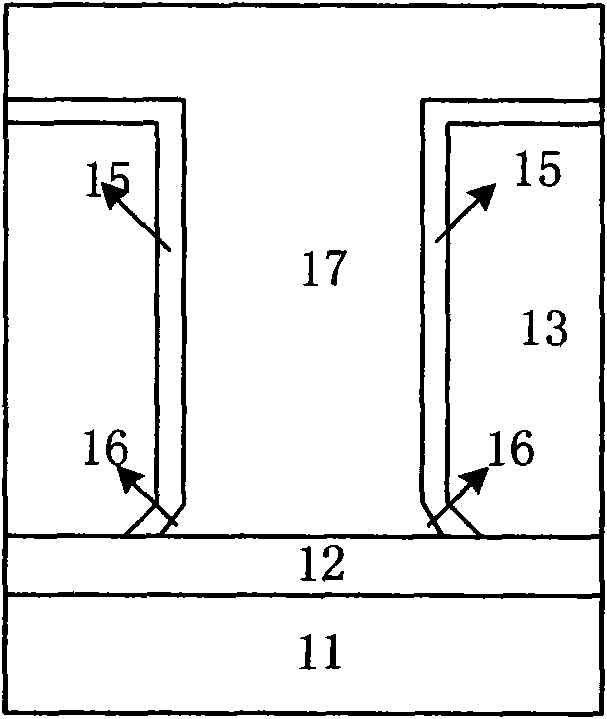

[0030] Please refer to diagram 2-1 , 2-2 , 2-3, 2-4, a silicon-on-insulator deep trench isolation structure adopting a new deep trench filling method, comprising: a semiconductor substrate 1, a buried oxide layer 22 is arranged on the semiconductor substrate 21, and the buried oxide N-type top layer silicon 23 is provided on layer 22, and the morphology of deep grooves is etched on the surface of N-type top layer silicon 23, and the deep groove structure is filled with dielectric, and the surface and side walls of N-type top layer silicon 23 are processed by dry oxygen method. Grow the first layer of oxide layer 24 with a thickness of 100-200 Deposit the first layer of polysilicon 26 on the sidewall of the first layer of oxide layer 24 grown by dry oxygen method, with a thickness of about 13% to 20% of the groove width, and to a greater extent depends on the lateral overetching of the bottom of the deep groove. The size of the polysilicon 26 does not have any doping, and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com