3D conduction structure and manufacturing method thereof

A technology of conducting structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor device, electric solid-state device and other directions, can solve the problems of easy hole expansion leakage current, large hole diameter at the end of channel 17, exposed chips, etc., and achieves shrinkage. Package volume, avoid inaccurate alignment, and shorten the effect of wire paths

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

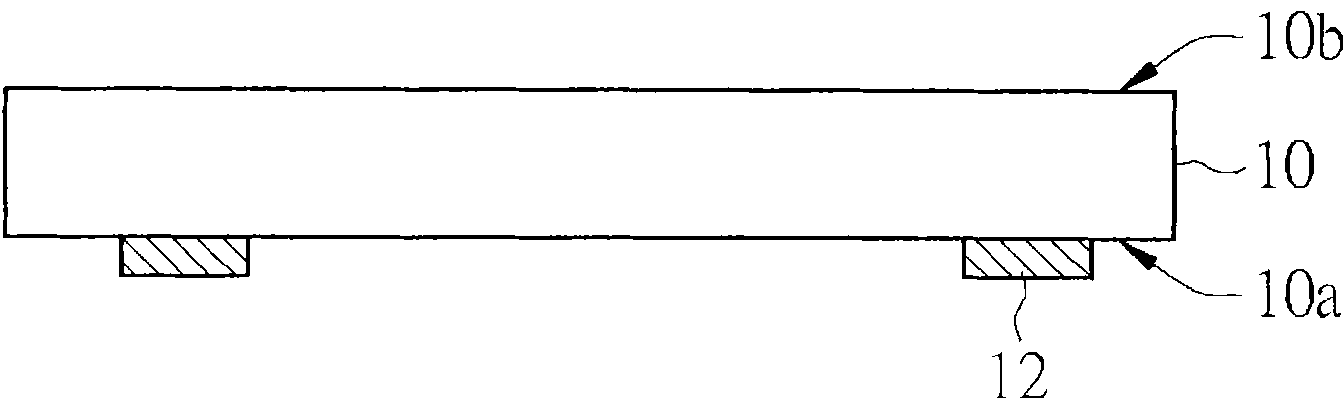

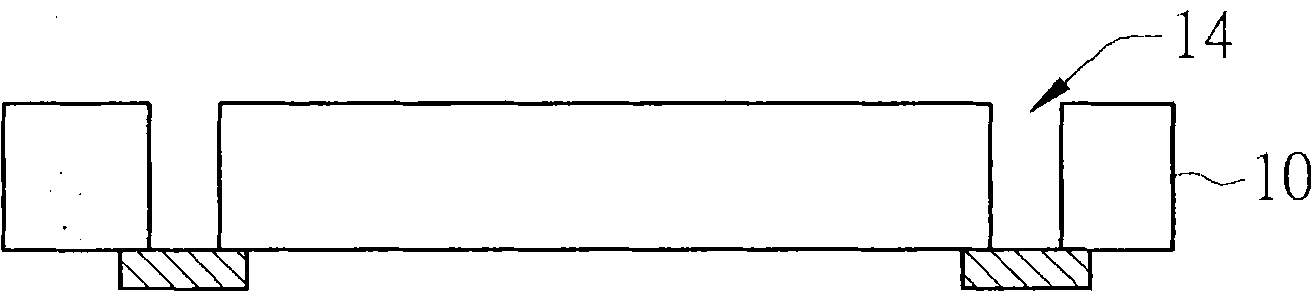

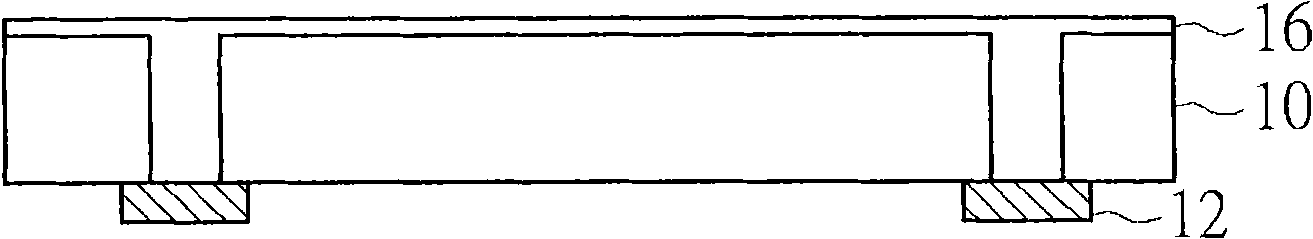

[0064] Please refer to Figure 2A-2J , which shows a manufacturing flow chart of the package with the three-dimensional conducting structure according to the first embodiment of the present invention. The manufacturing method of the package with the three-dimensional conducting structure of this embodiment includes the following steps. First, please refer to Figure 2A , providing a first substrate 110 , the first substrate 110 has an active surface 112 and a passive surface 114 opposite thereto, and the first substrate 110 has solder pads 116 located on the active surface 112 . The first substrate 110 is preferably an image sensor chip (CMOS Image Sensor, CIS), which receives images or light through the active surface 112 .

[0065] After that, a hole is drilled from the active surface 112 of the first substrate 110 to the passive surface 114, thereby forming a through hole 118. The through hole 118 can be arranged at any position of the first substrate 110, for example, it...

no. 2 example

[0082] The difference between this embodiment and the above-mentioned embodiments lies in the position of the through hole, the structure of the first redistributed conductor and its forming method. The rest of the same components and steps use the same reference numerals and will not be repeated here.

[0083] Please refer to FIGS. 4A-4E , which are schematic diagrams showing the manufacturing process of the package with the three-dimensional conducting structure according to the second embodiment of the present invention. Referring to FIG. 4A , the first substrate 110 has a solder pad 116 on its active surface 112 and has a through hole 218 . Next, a first redistribution conductor is formed on the active surface 112 of the first substrate 110 , and the steps are described as follows.

[0084] First, as shown in FIG. 4A , a conductive bump 228 is formed on the active surface 112 of the first substrate 110 , such as by electroplating or printing. The conductive bump 228 protr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com