Methods of forming through-substrate interconnects

A substrate and semiconductor technology, applied in semiconductor devices, electrical components, nanotechnology, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

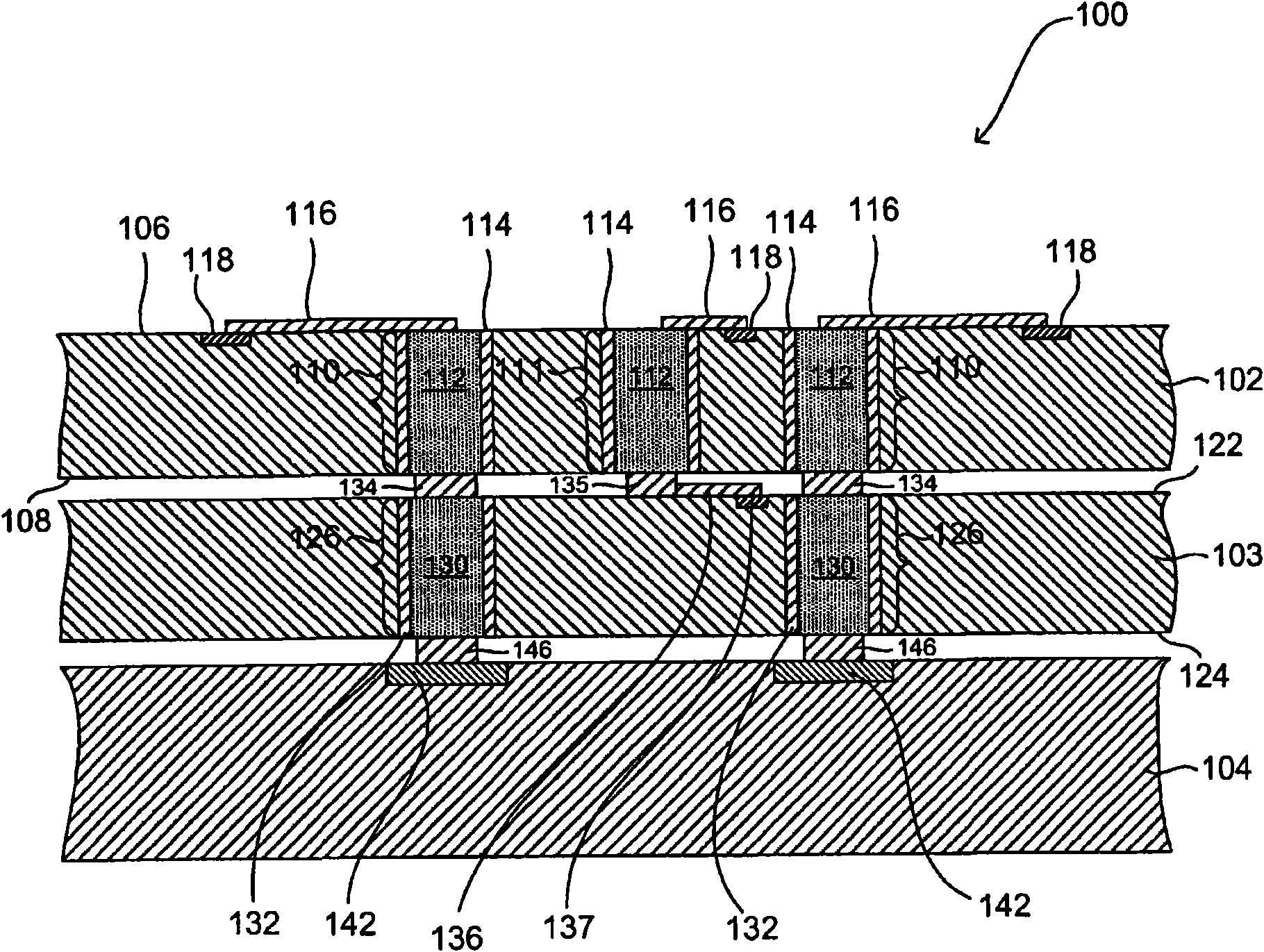

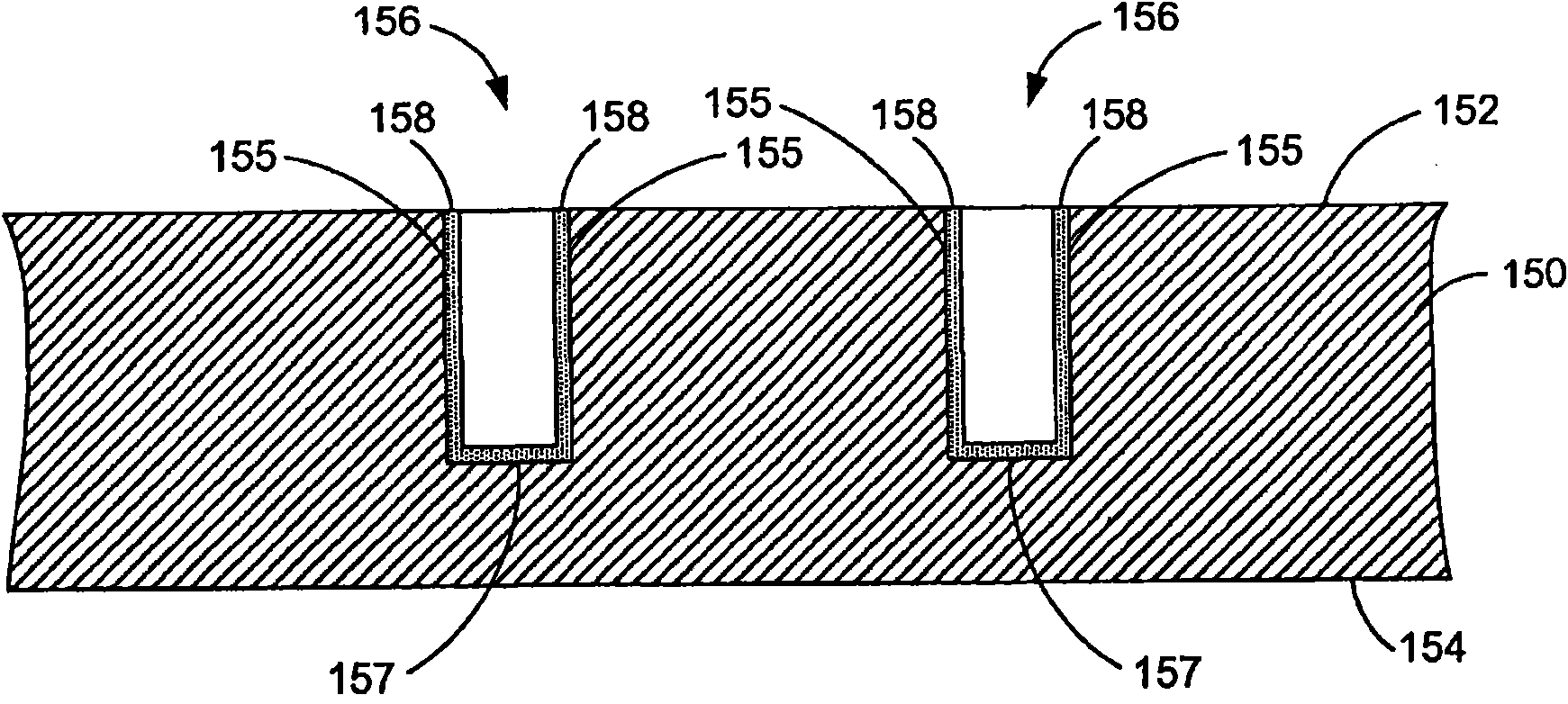

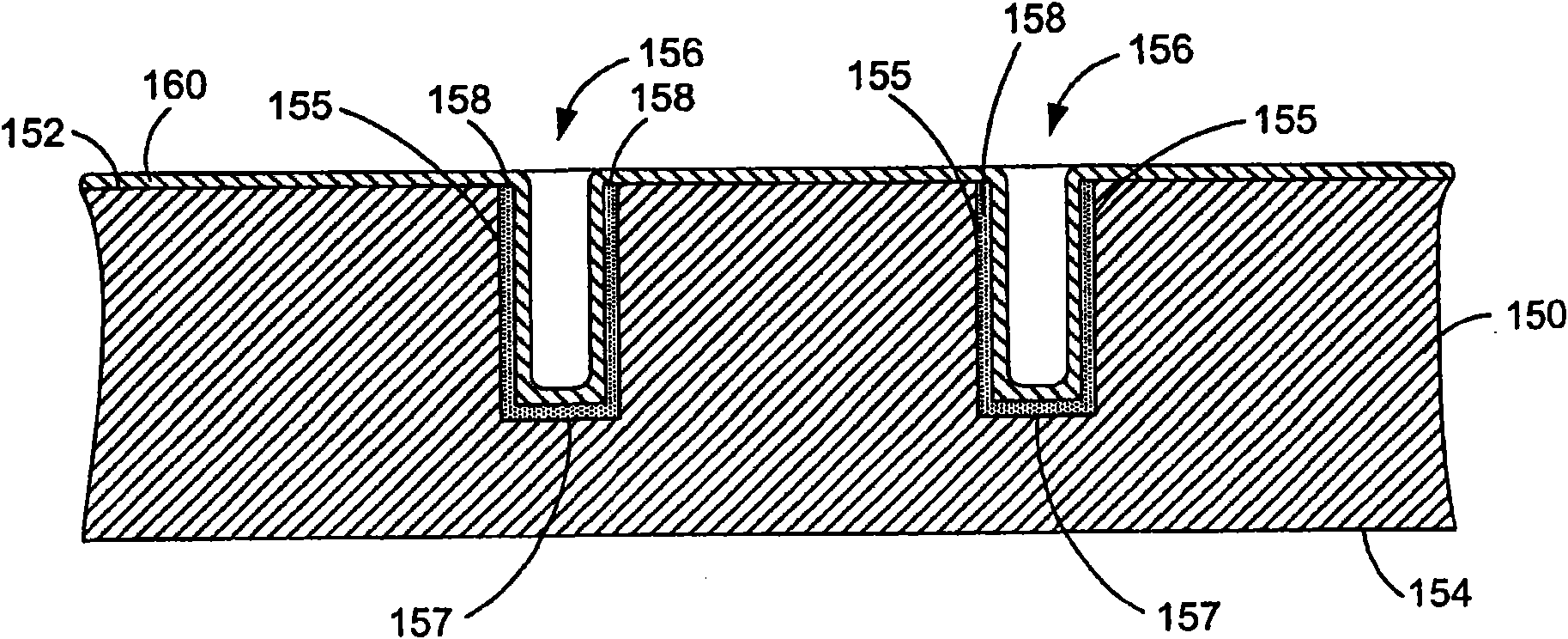

[0015] Various embodiments of the invention relate to methods of forming through-substrate interconnects. Figures 3A to 3K Illustrated is a method of forming at least one through-substrate interconnect according to an embodiment of the present invention, wherein at least one opening formed in a semiconductor substrate is filled with a conductive material grown in the presence of metal catalyst nanoparticles. Such as Figure 3A As shown, a semiconductor substrate 200 having an active face 202 and an opposite back face 204 is provided. The active face 202 includes a number of contact regions 206 (only two are shown for simplicity), each of which is electrically connected to an active semiconductor device (e.g., a transistor) and / or a passive element (e.g., a capacitor, resistor, or other passive components), the above-mentioned active semiconductor devices are located in the active region 208 formed under the active surface 202 , and the above-mentioned passive components can ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com