Stacked integrated circuit and manufacturing method thereof

一种集成电路、堆叠式的技术,应用在电路、半导体/固态器件制造、电气元件等方向,能够解决一般产品及方法没有适切结构及方法、不便等问题,达到产品可靠度改善、技术进步的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

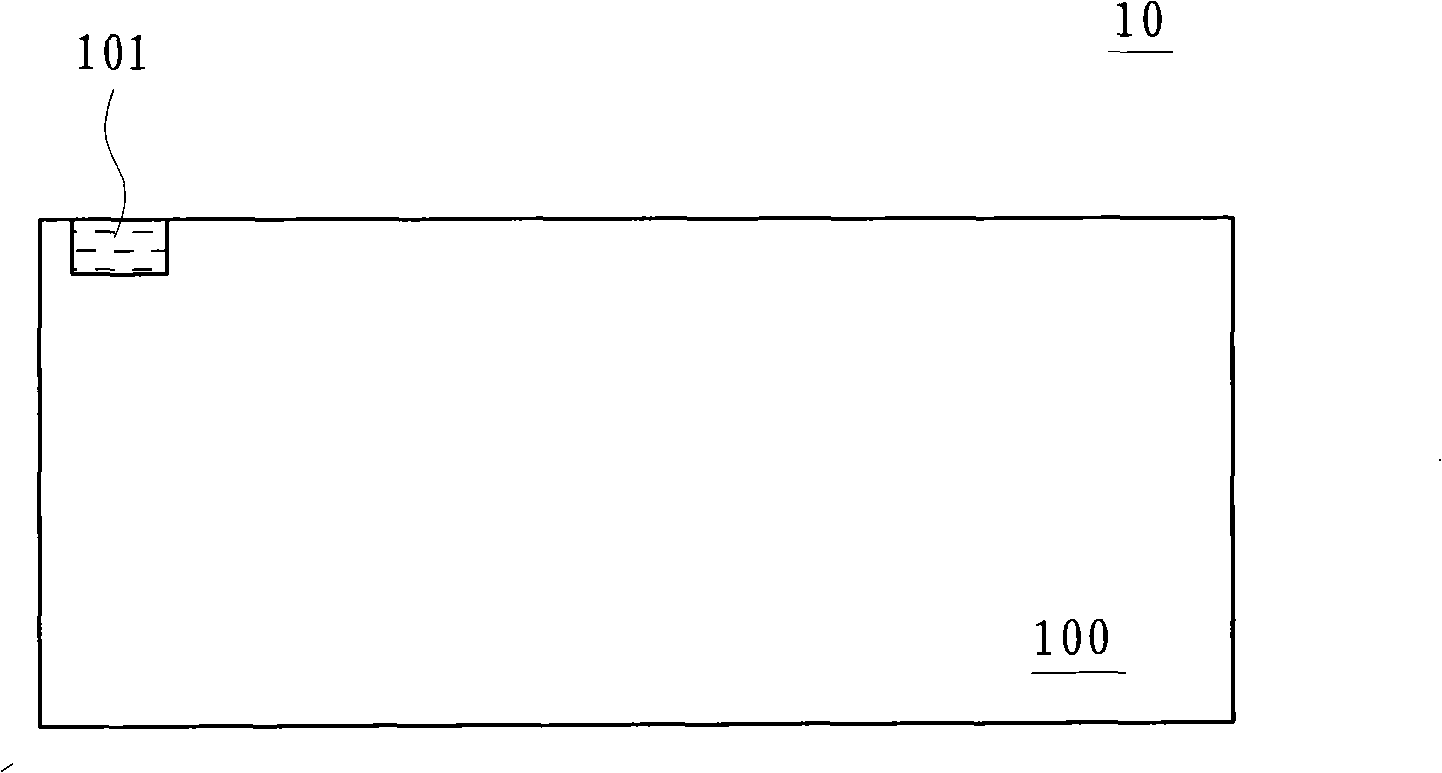

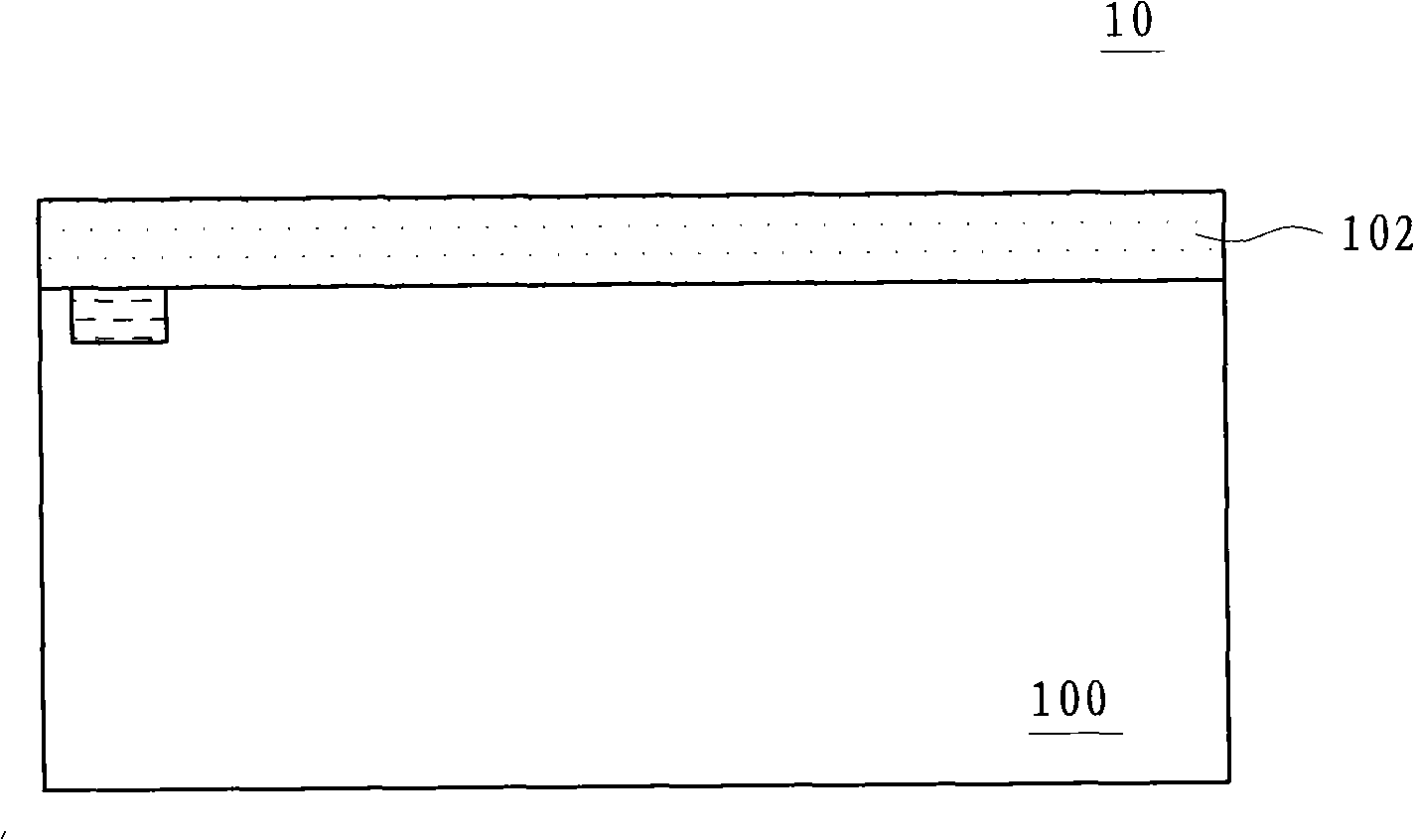

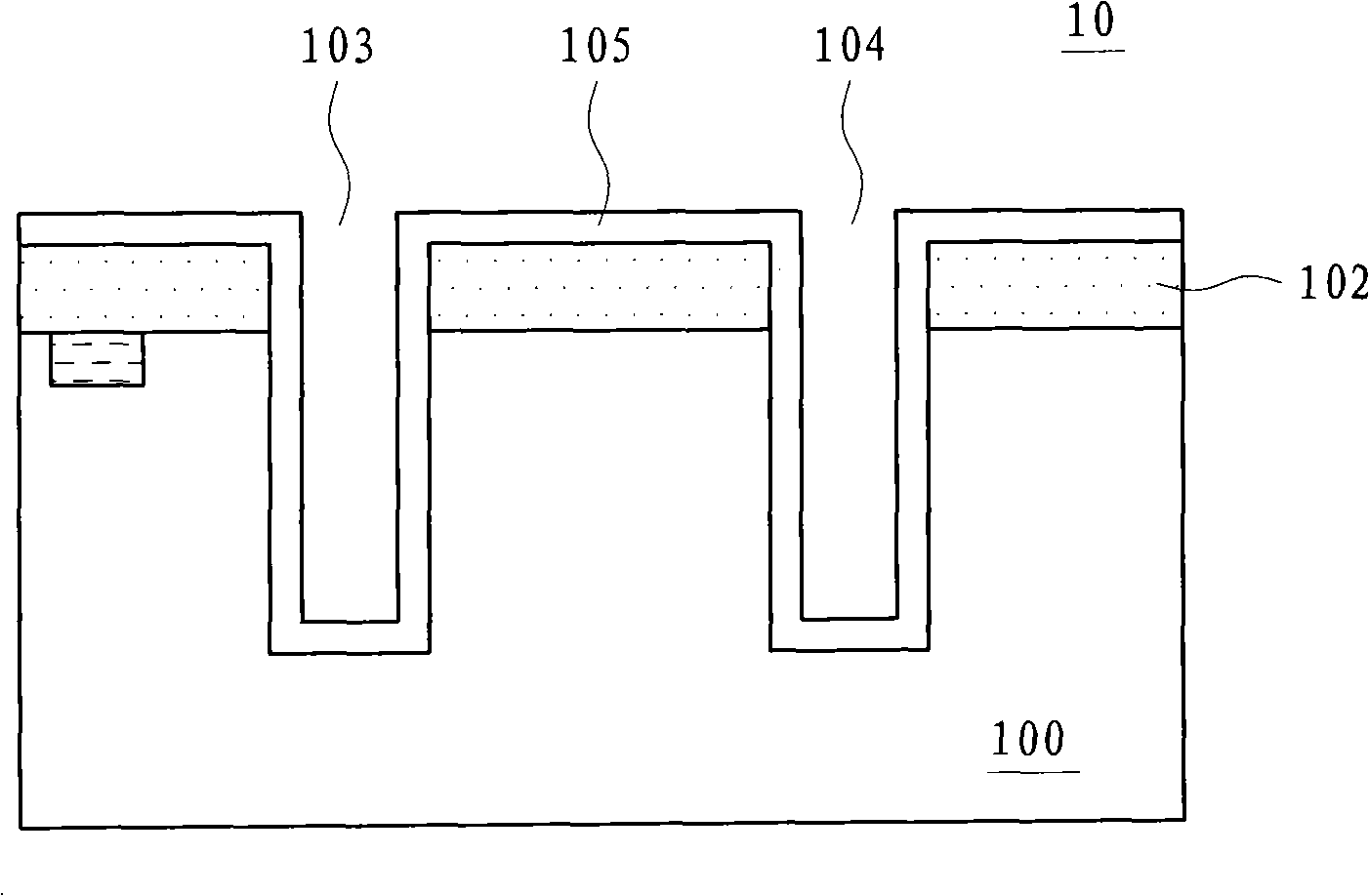

[0087] In order to further explain the technical means and effects of the present invention to achieve the intended purpose of the invention, the specific implementation, structure and method of the stacked integrated circuit and its manufacturing method proposed according to the present invention will be described below in conjunction with the accompanying drawings and preferred embodiments. , steps, features and effects thereof are described in detail below.

[0088] The aforementioned and other technical contents, features and effects of the present invention will be clearly presented in the following detailed description of preferred embodiments with reference to the drawings. Through the description of the specific implementation mode, when the technical means and functions adopted by the present invention to achieve the predetermined purpose can be obtained a deeper and more specific understanding, but the accompanying drawings are only for reference and description, and ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com