Method for constructing network on three-dimensional chip

An on-chip network and network structure technology, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve the problems of low throughput rate, large network delay, etc., achieve high throughput rate, small network delay, and simple implementation Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

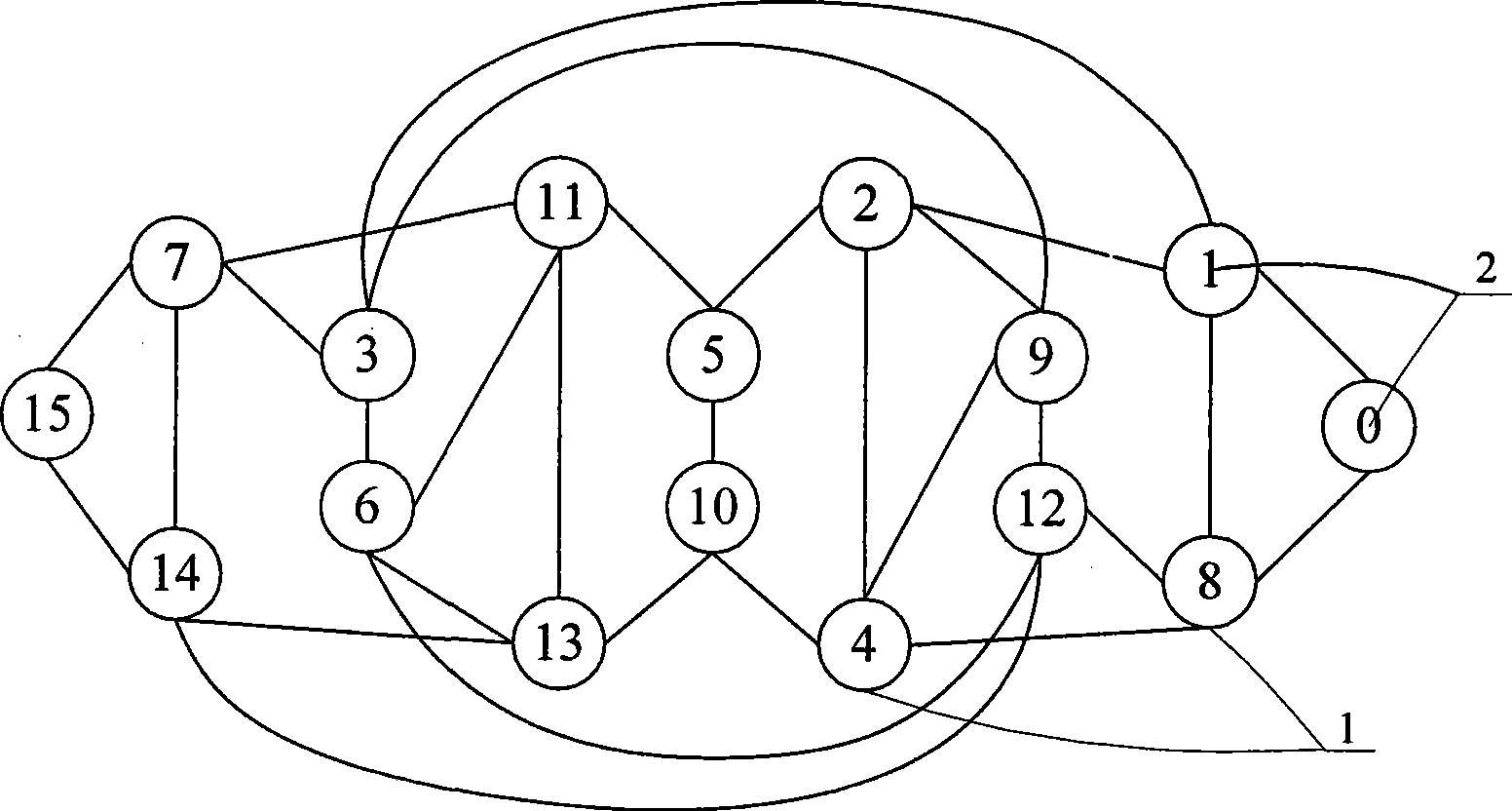

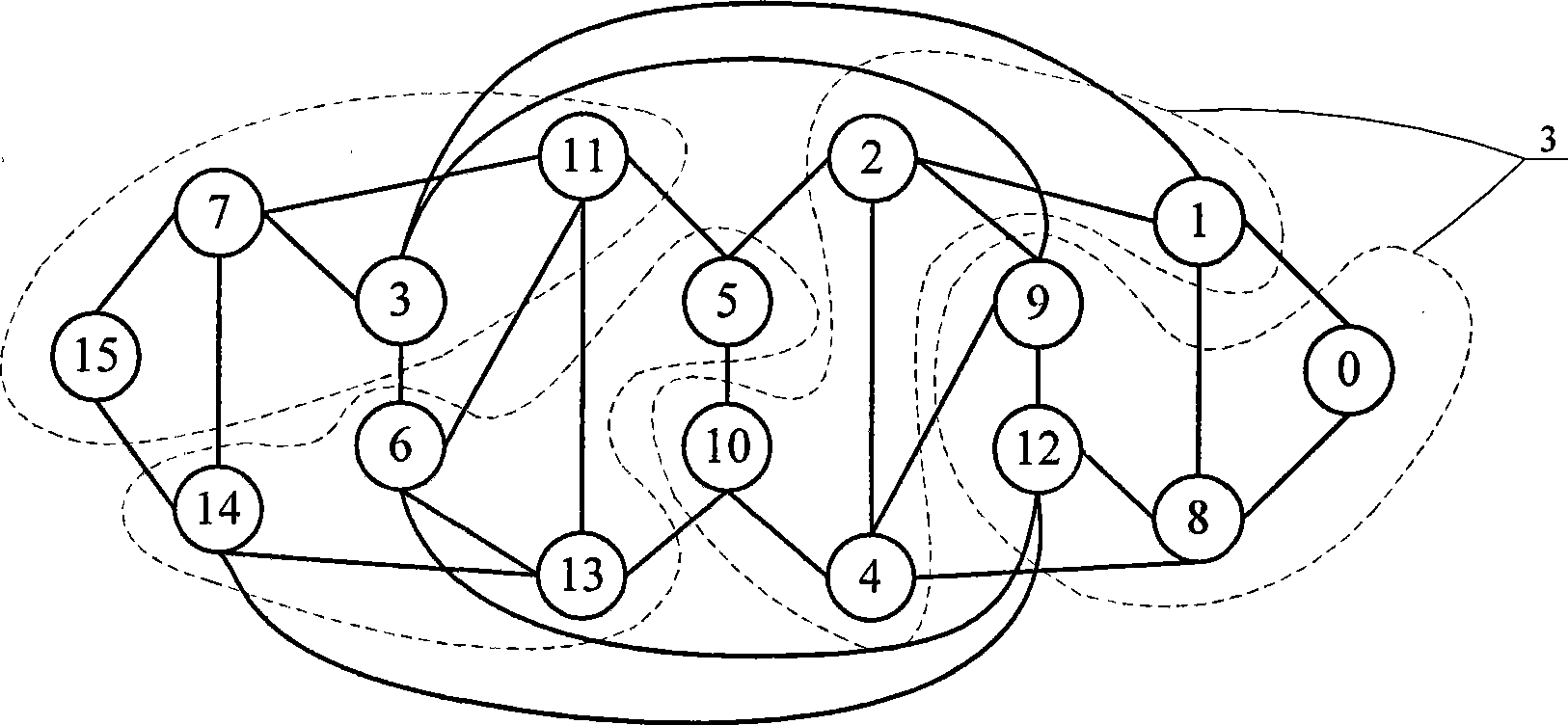

[0035] Network topology: the three-dimensional NoC in Embodiment 1 of the present invention is structured as follows: its horizontal plane network and virtual plane network are both De Bruijn graph structures, and the number of nodes on each horizontal plane network is equal. Each The number of nodes on the virtual plane is also equal. The horizontal number and virtual plane number of each node are arranged according to the construction method of De Bruijn diagram. In order to reduce the complexity of layout and wiring in the chip, the division of nodes that constitute each virtual plane It should be possible to utilize the existing connections on the horizontal network as much as possible. Taking a 4-layer horizontal plane network with 16 nodes on each plane as an example, divide it in the following way: Divide the De Bruijn graph on each horizontal plane network into four Hamiltonian roads each containing 4 nodes, which are respectively recorded as HA, HB, and HC and HD, whe...

Embodiment 2

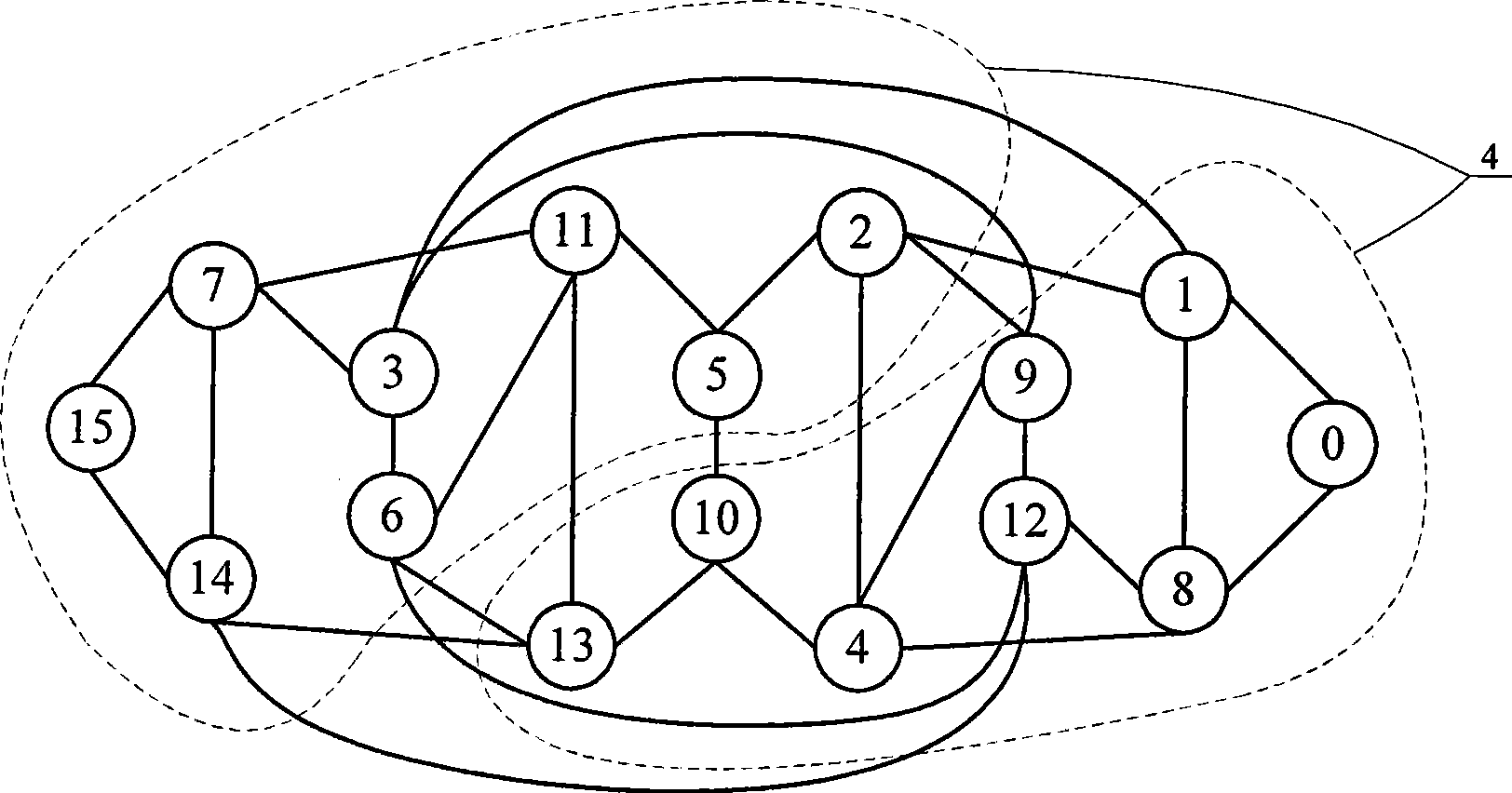

[0072] The virtual plane division method in this embodiment is: divide all the nodes in the network into two virtual planes, each virtual plane adopts a ring topology. Because there are two imaginary planes, all nodes are connected into two rings, that is, a double ring is formed, and the division of the double ring is carried out as follows:

[0073] First, divide all the nodes in the horizontal network of each layer into two Hamilton roads, which are respectively recorded as HA and HB. The starting point and end point of the two roads of HA and HB must be adjacent to each other; The number of nodes of each is N, image 3 It shows a double-ring division method with 16 nodes on each plane, nodes 0, 1, 4, 8, 9, 10, 12 and 13 belong to ring 1, and the remaining nodes belong to ring 2.

[0074] Then, the HAs of each layer are connected into a ring, and the HBs are connected into another ring, and each ring is a virtual plane. The way each ring is formed is as follows:

[0075]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com