Method for implementing reconfigurable accelerator custom-built for program

An implementation method and accelerator technology, applied in the direction of program control devices, etc., can solve the problems of low utilization rate and flexibility, increase design cost, etc., and achieve the effect of reducing execution cycle, maintaining flexibility and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

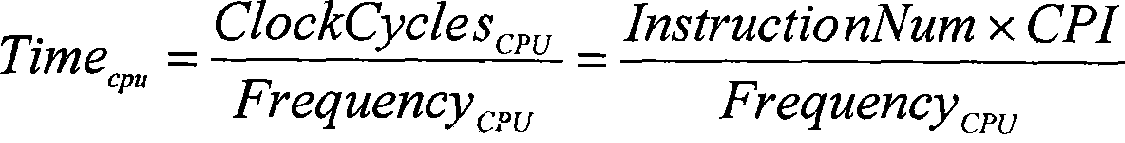

Method used

Image

Examples

Embodiment Construction

[0031] The specific implementation process of the reconfigurable accelerator implementation method customized for programs is as follows.

[0032] 1) Add reconfigurable accelerator-assisted computing:

[0033] On the traditional general-purpose computer system, FPGA is added as a reconfigurable component, and the FPGA is connected to the traditional computer system through the PCI-E bus.

[0034] The reconfigurable accelerator is responsible for processing the calculation-intensive part of the program and accepts the call of the program. After the program calls the reconfigurable accelerator, the reconfigurable accelerator starts to process the input data. During the calculation of the reconfigurable accelerator, the program hangs; when After the execution of the reconfigurable accelerator is completed, the result is returned to the program, and the program continues to execute.

[0035] 2) The program customizes the implementation process of the reconfigurable accelerator, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com