Double-stage self-aligning contact window and manufacturing method thereof

A manufacturing method and contact window technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., to achieve the effects of avoiding incomplete opening, increasing process space, and increasing production

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

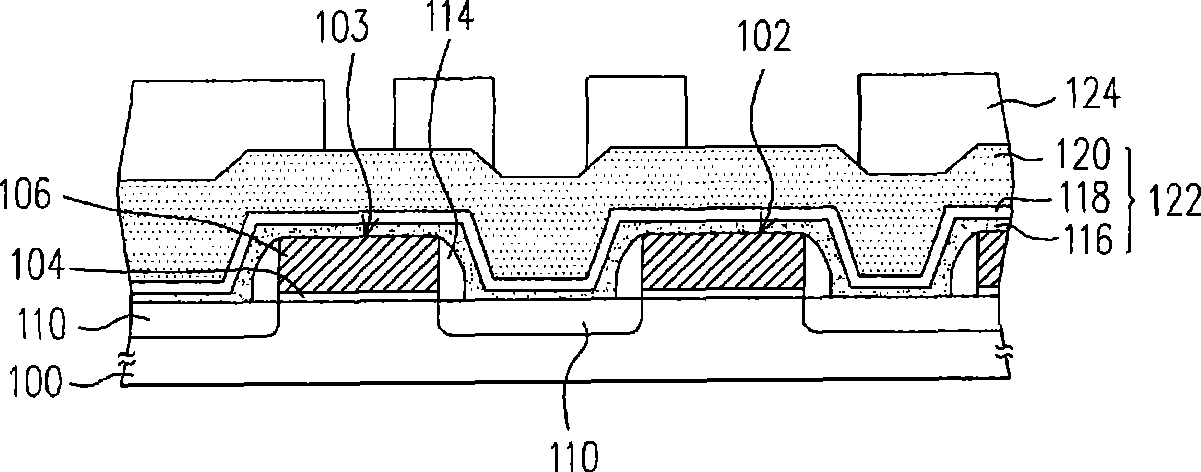

[0054] Figure 2A to Figure 2F It is a flow sectional view of a method for manufacturing a semiconductor device according to an embodiment of the present invention.

[0055] Please refer to Figure 2A , first provide a substrate 100 . The substrate 100 is, for example, a silicon substrate, such as an N-type silicon substrate or a P-type silicon substrate. Certainly, the substrate 100 may also be a substrate with silicon on an insulating layer or the like. Transistors 102 and 103 have been formed on the substrate 100 . The transistors 102 and 103 are, for example, N-channel metal oxide semiconductor devices (NMOS) or P-channel metal oxide semiconductor devices (PMOS).

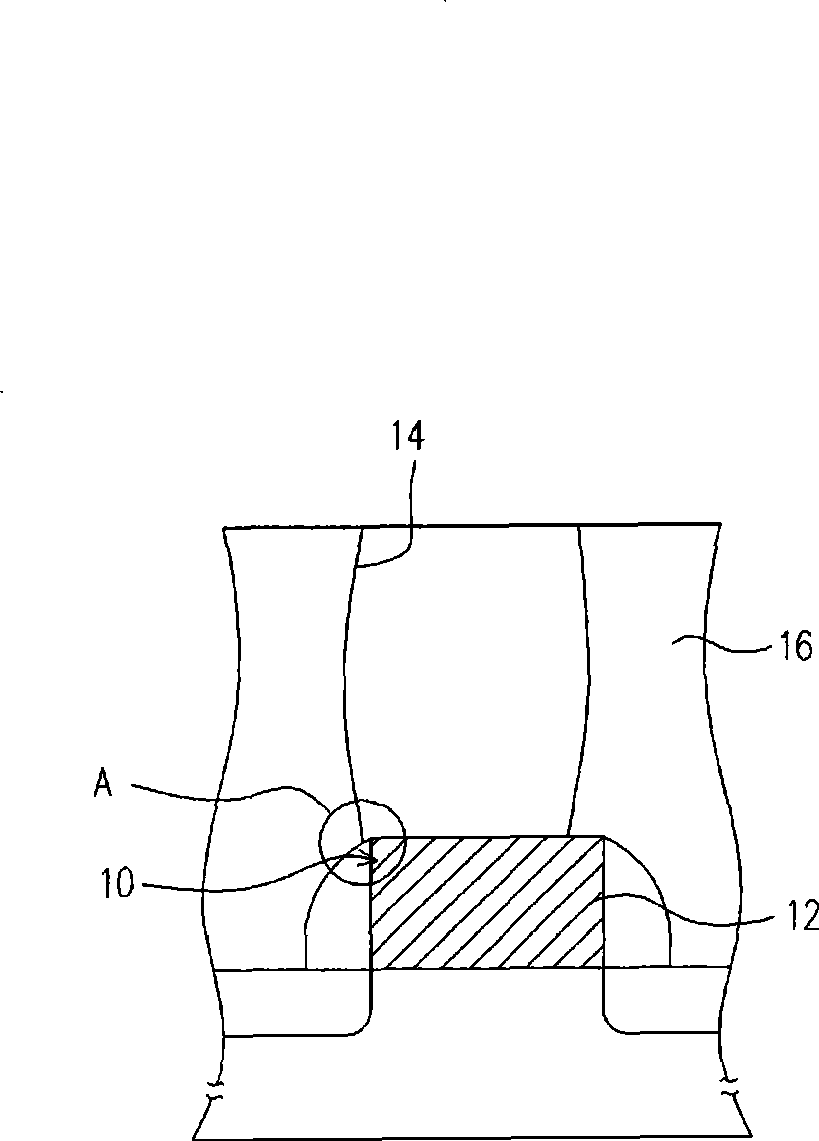

[0056] The transistors 102 and 103 are formed by a gate dielectric layer 104 , a gate 106 , a spacer 114 and a source / drain region 110 , respectively. The gate dielectric layer 104 is located between the gate 106 and the substrate 100 . The material of the gate dielectric layer 104 may be composed of a sil...

Embodiment 2

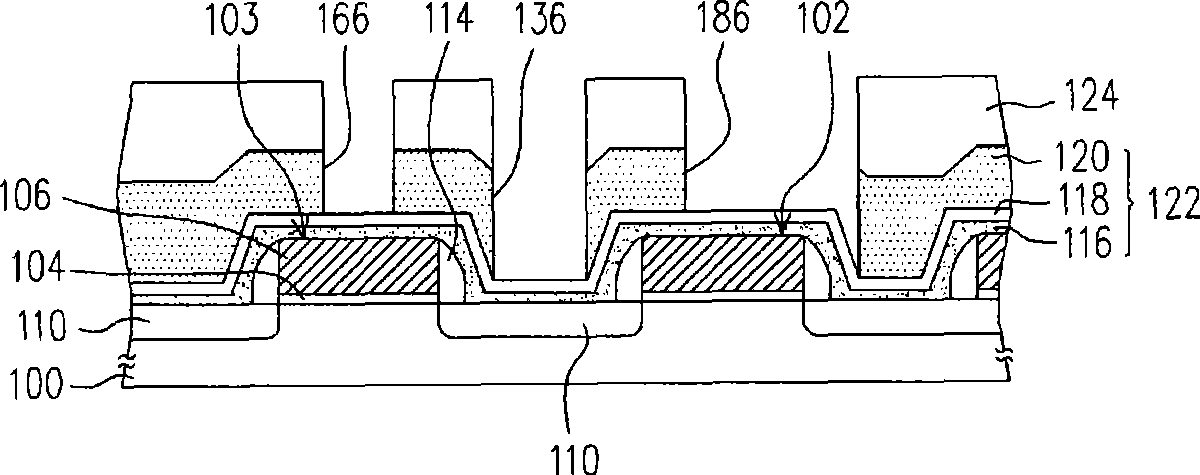

[0074] Figures 3A to 3H It is a flow sectional view of another method for manufacturing a semiconductor device according to an embodiment of the present invention.

[0075] Please refer to Figure 3A and 3B , according to the method described in the embodiment, the dielectric layer 122 on the substrate 100 is subjected to a first-stage patterning process, so as to form a lower opening 136 corresponding to the source / drain region 110 in the dielectric layer 122, The lower opening 166 corresponds to the gate 106 of the transistor 103 and the lower opening 186 corresponds to the gate 106 of the transistor 102 and the source / drain region 110 of the transistor 103 .

[0076] Please refer to Figure 3C After removing the photoresist layer 124 , a conformal liner material layer 150 is first formed on the substrate 100 to cover the dielectric layer 122 and the sidewalls and bottoms of the lower openings 136 , 166 and 186 . The material of the liner material layer 150 includes sil...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com