Debug method suitable for multi-processor core system chip

A technology of multi-processor cores and system chips, which is applied in the debugging field of multi-processor core system chips, can solve the problems of low intrusion, high hardware cost, and slow debugging speed, and achieve low hardware cost and strong portability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

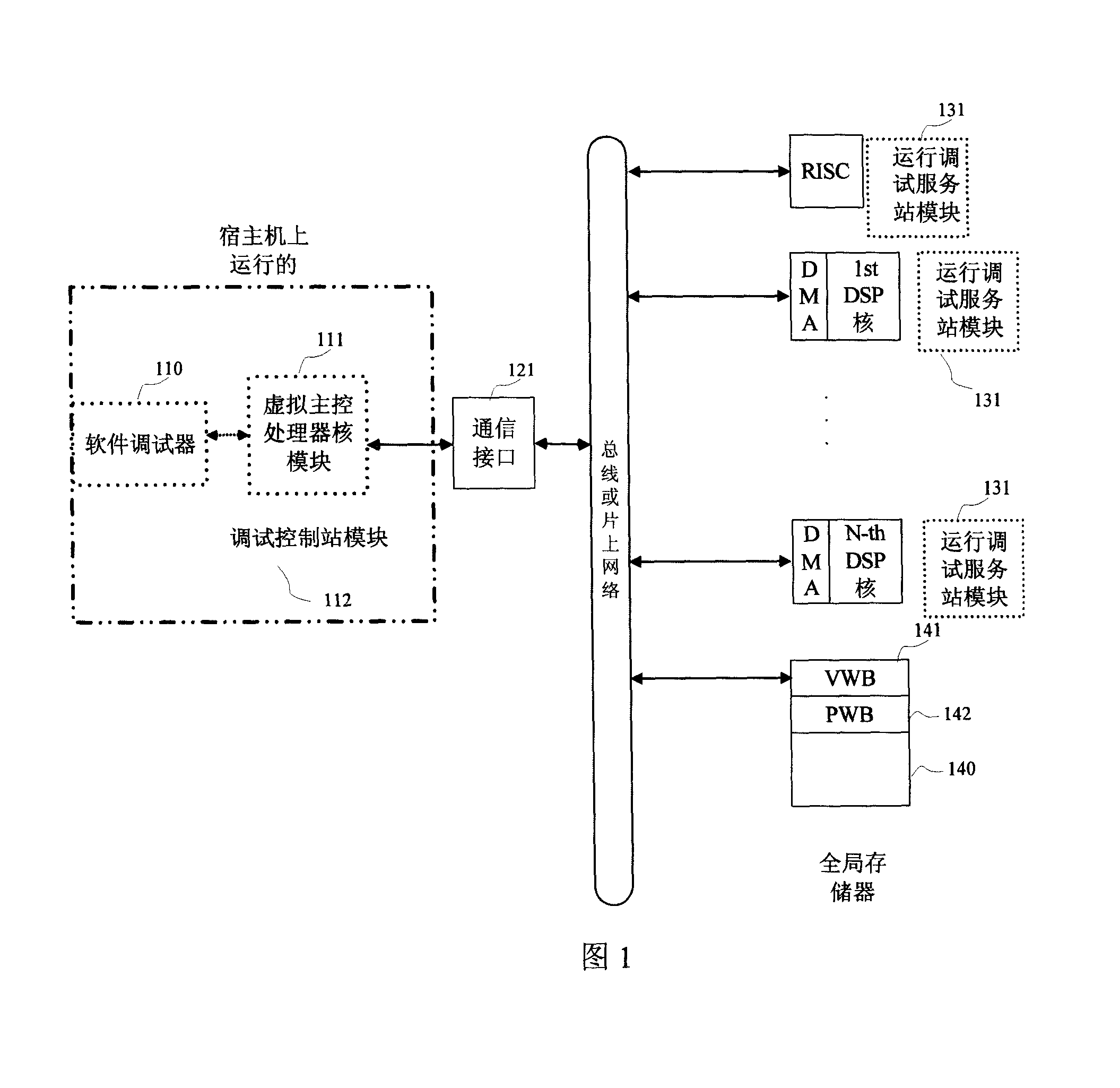

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

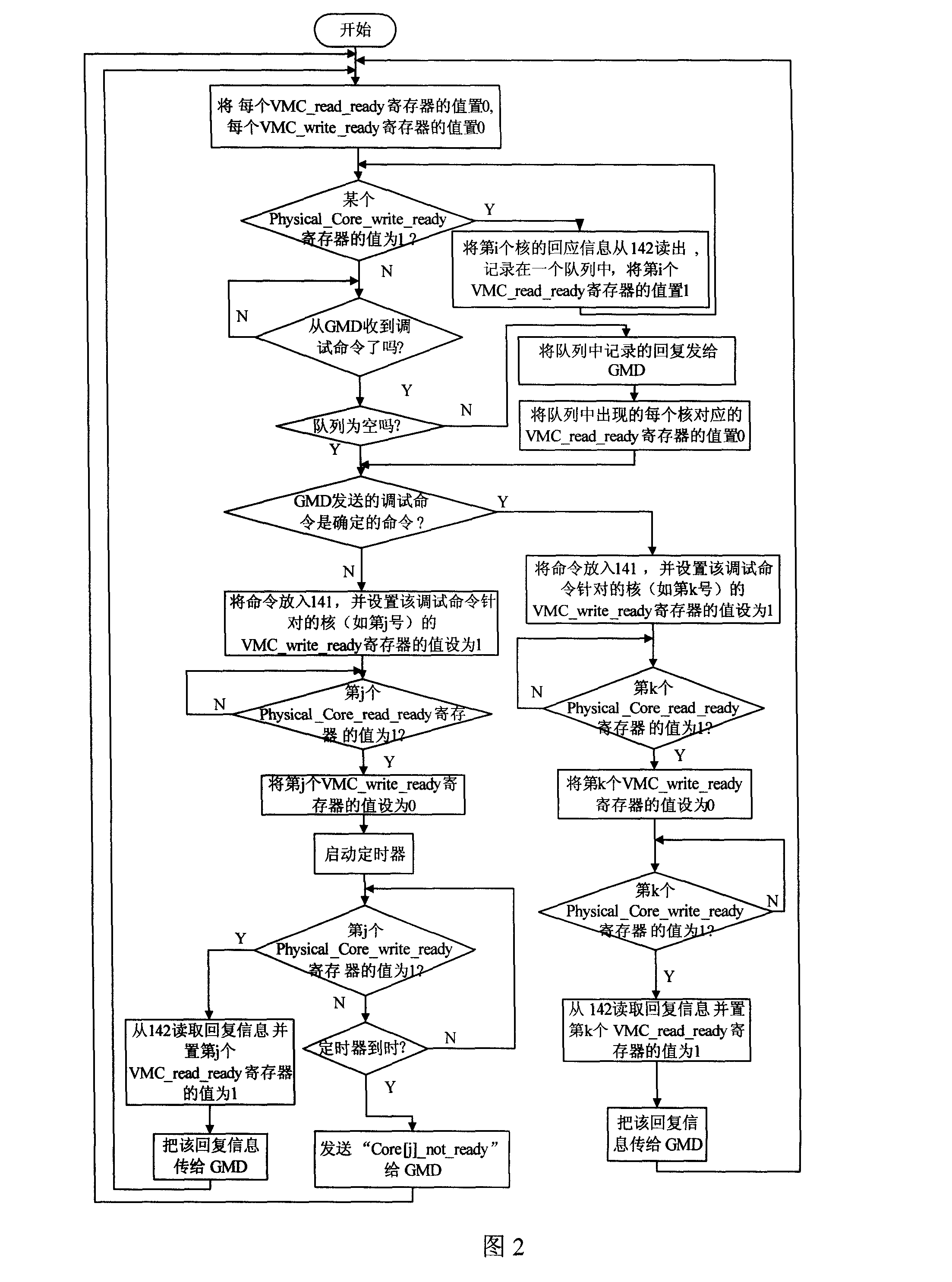

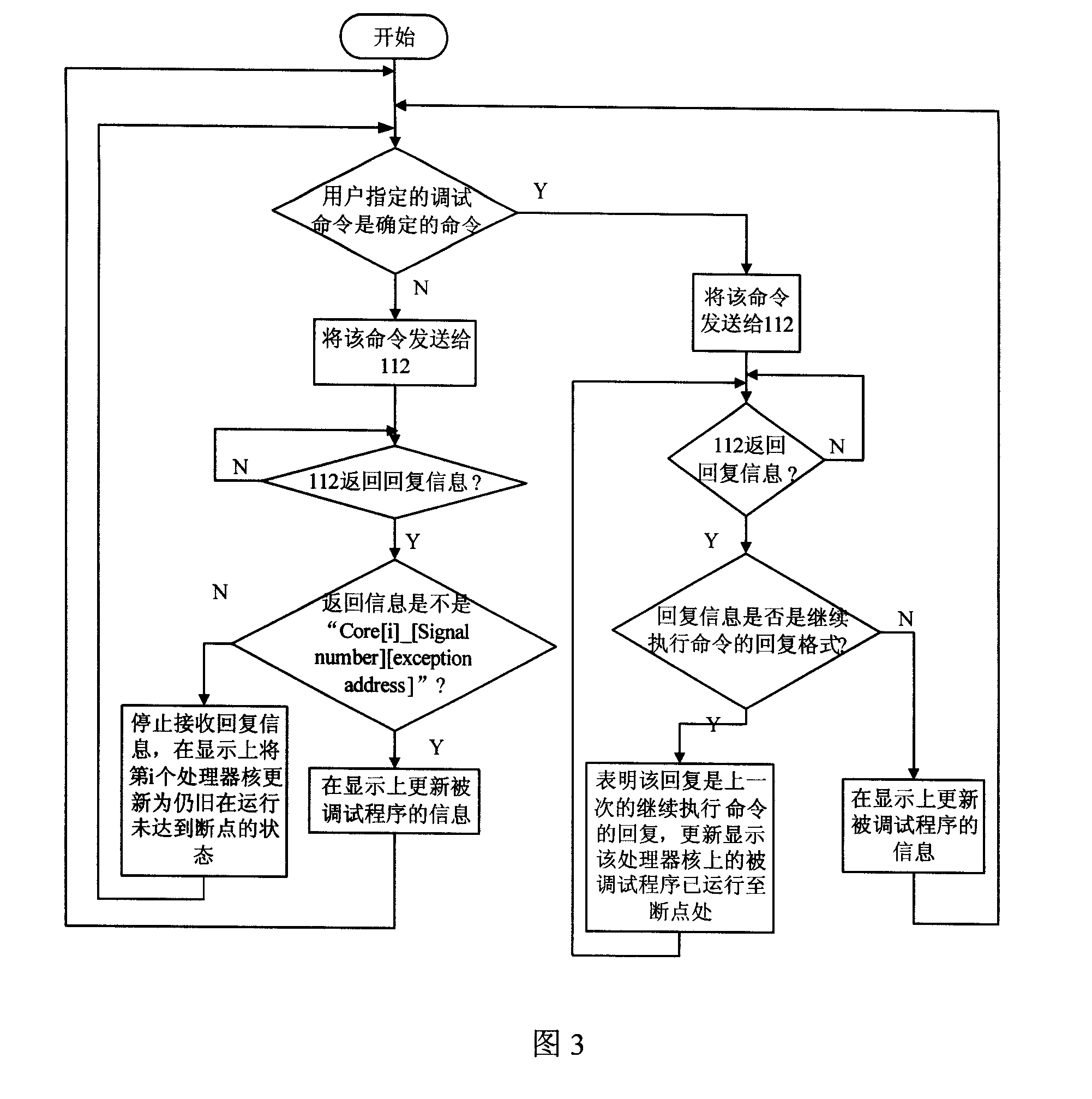

Embodiment Construction

[0027]The format of the present invention's definition debugging command packet and return information packet is: processor core number, thread number (optional), basic command (or return packet basic format), as follows:

[0028] Step through:

[0029] MP_step = {C1_s, C2_s, ..., {C i _thread1_s, C i _thread2_s,...},...}

[0030] Return_MP_step = {C1_S_address, C2_S_address, ...,

[0031] {C i _thread1_S_address, C i _thread2_S_address,...},...}

[0032] Add breakpoint:

[0033] MP_add_break = {C1_z_address, C2_z_address, ...,

[0034] {C i _thread1_z_address, C i _thread2_z_address...},...}

[0035] Return_MP_add_break = {C1_zOK, C2_zOK, ...,

[0036] {C i _thread1_zOK,C i _thread2_zOK...},...}

[0037] Remove breakpoint:

[0038] MP_delete_break = {C1_Z_address, C2_Z_address, ...,

[0039] {C i _thread1_Z_address, C i _thread2_Z_address,...},...}

[0040] Return_MP_delete_break = {C1_ZOK, C2_ZOK, ...,

[0041] {C i _thread1_ZOK,C i _thread2_ZOK...},......

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com