Processor instruction set supporting part statement function of higher order language

A technology of processor instruction and high-level language, which is applied in the direction of electrical digital data processing, instruments, memory systems, etc., can solve problems such as memory performance bottlenecks, lack of direct support for high-level languages, complex instruction formats, etc., to facilitate compiler design, Avoid the large consumption of decoding time and simplify the effect of mapping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

[0020] The embodiment of the present invention takes the instruction format of the 64-bit fixed-length instruction set and the special instruction supporting the high-level language statement in the instruction set as an example, but is not limited to this example.

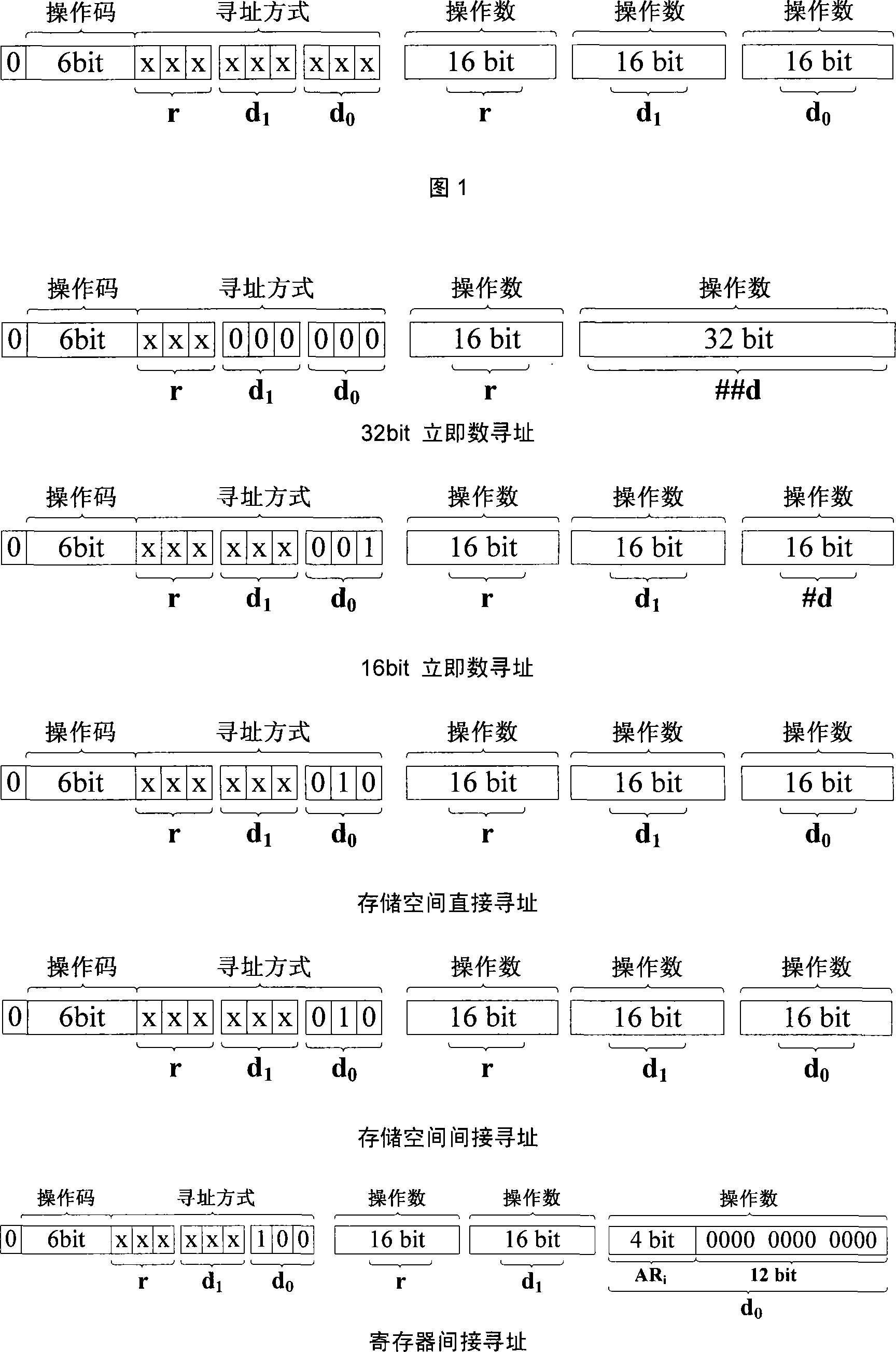

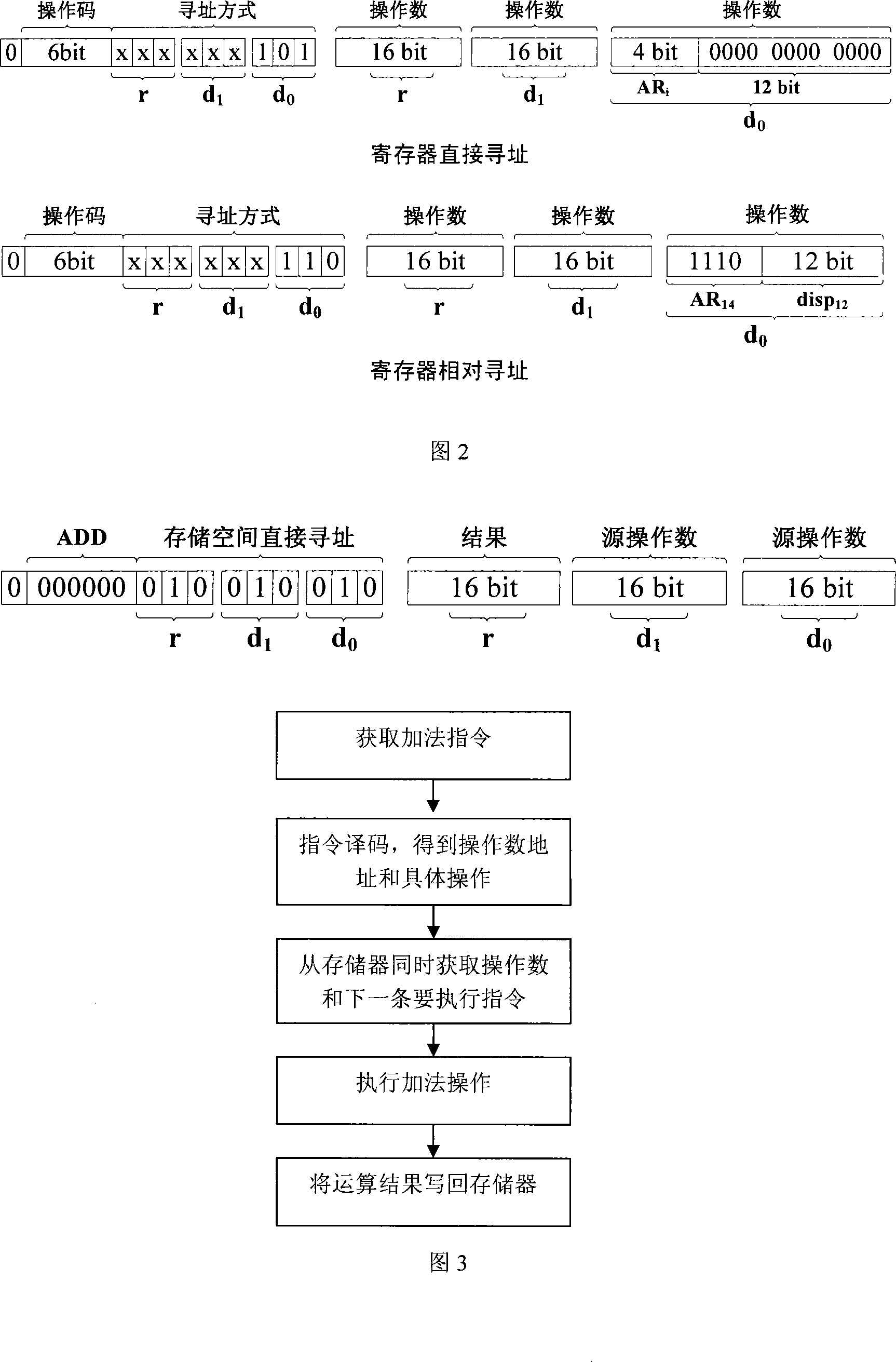

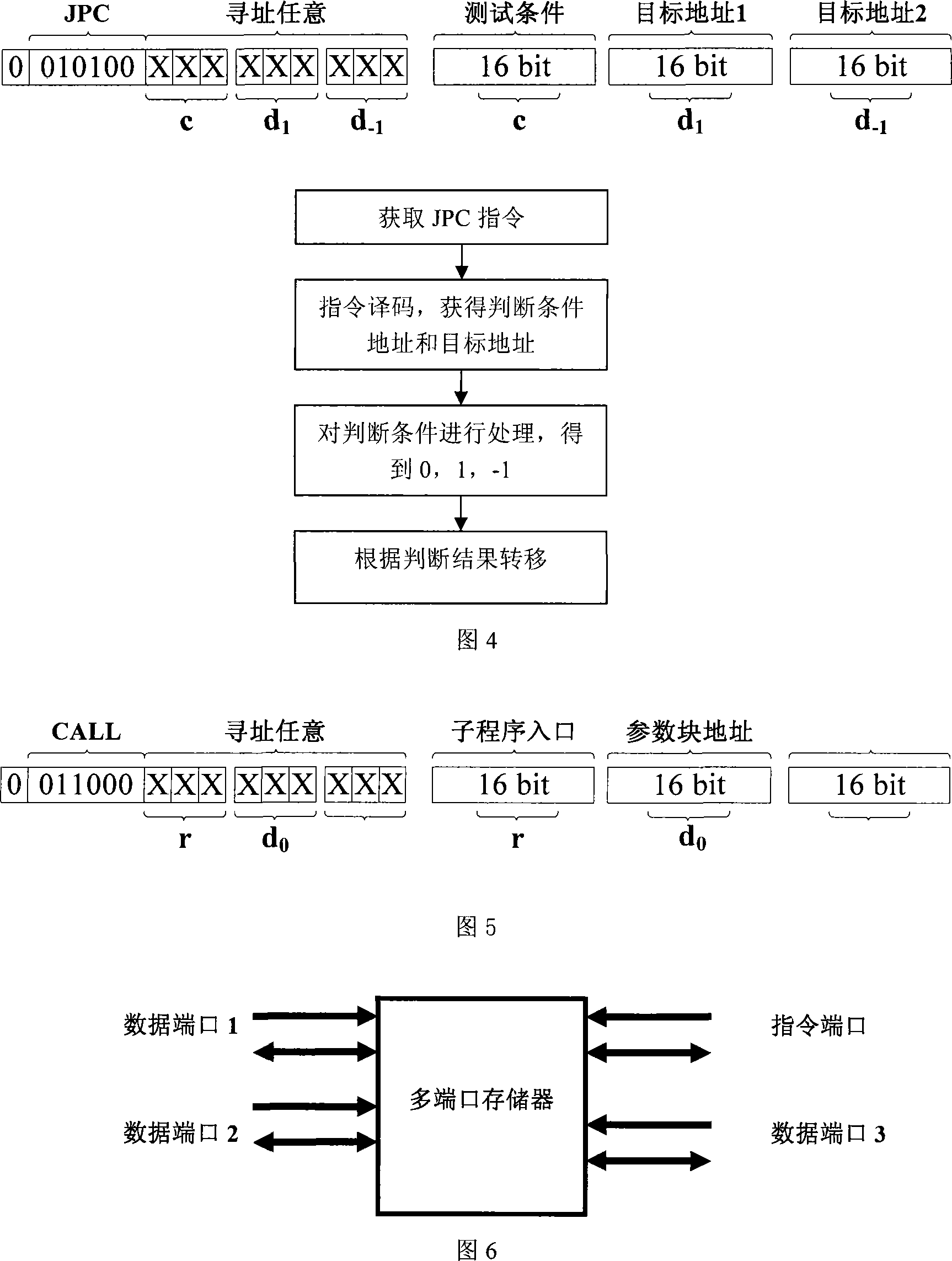

[0021] The basic encoding method of 64-bit instructions described in Figure 1 shows the instruction format. The instruction length is 64 bits, and the leftmost part contains 1 reserved bit, followed by the opcode field, addressing mode descriptor field, and address code field. The position of the opcode field is fixed, the length is determined to be 6 digits, the first digit is reserved, and the first 3 digits of the last 5 digits of the opcode are coded to distinguish the operation types, including addition and subtraction (000), multiplication and division (001), logic operations (010), a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com