Method for making non-volatile memory

A non-volatile and manufacturing method technology, applied in the field of non-volatile memory manufacturing, can solve the problems of increased production cost of process steps, increased total thickness of dielectric layers, increased element resistance value, etc., so as to avoid the element resistance value. The effect of increasing, decreasing the total thickness, reducing the number of masks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

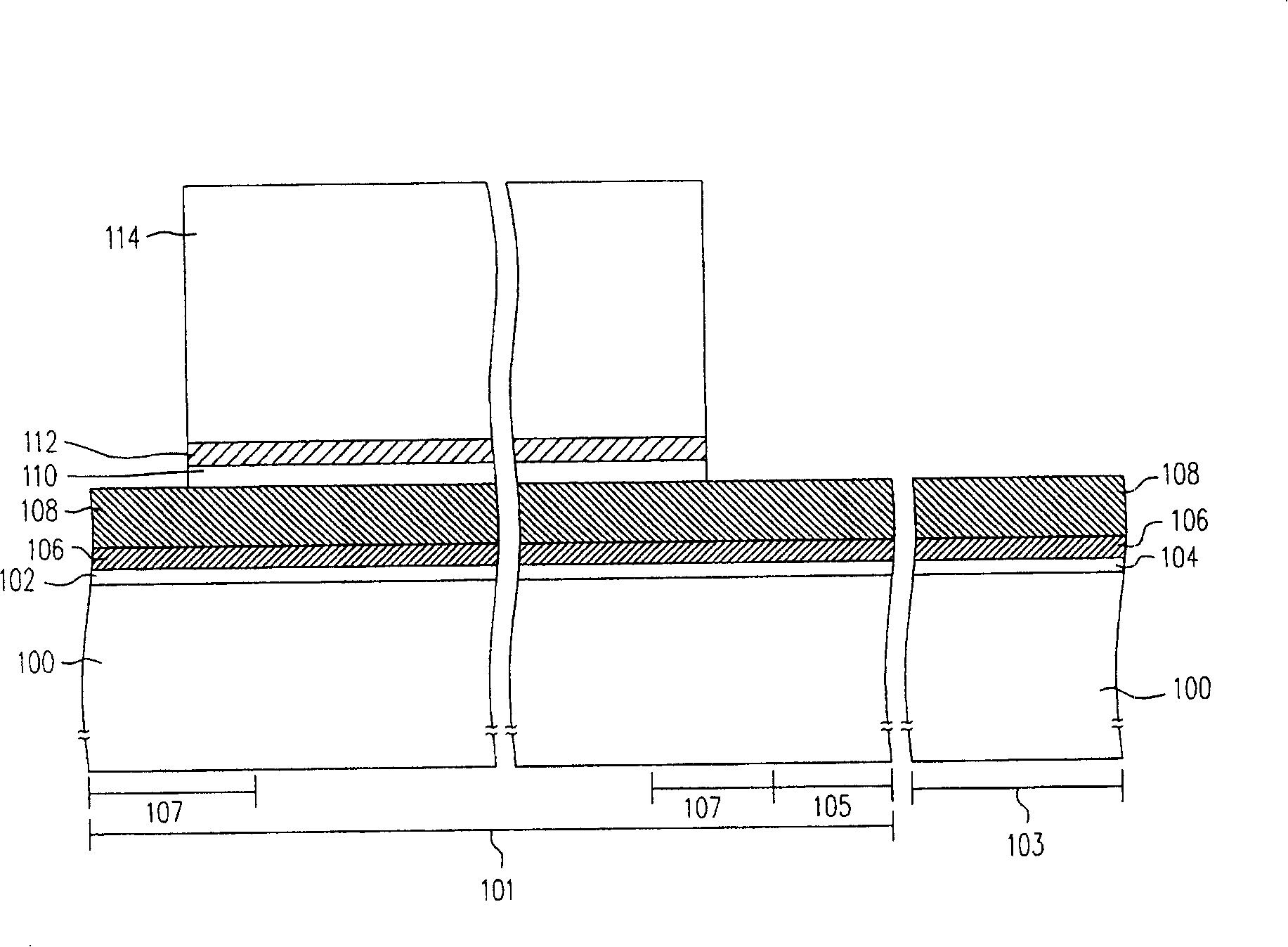

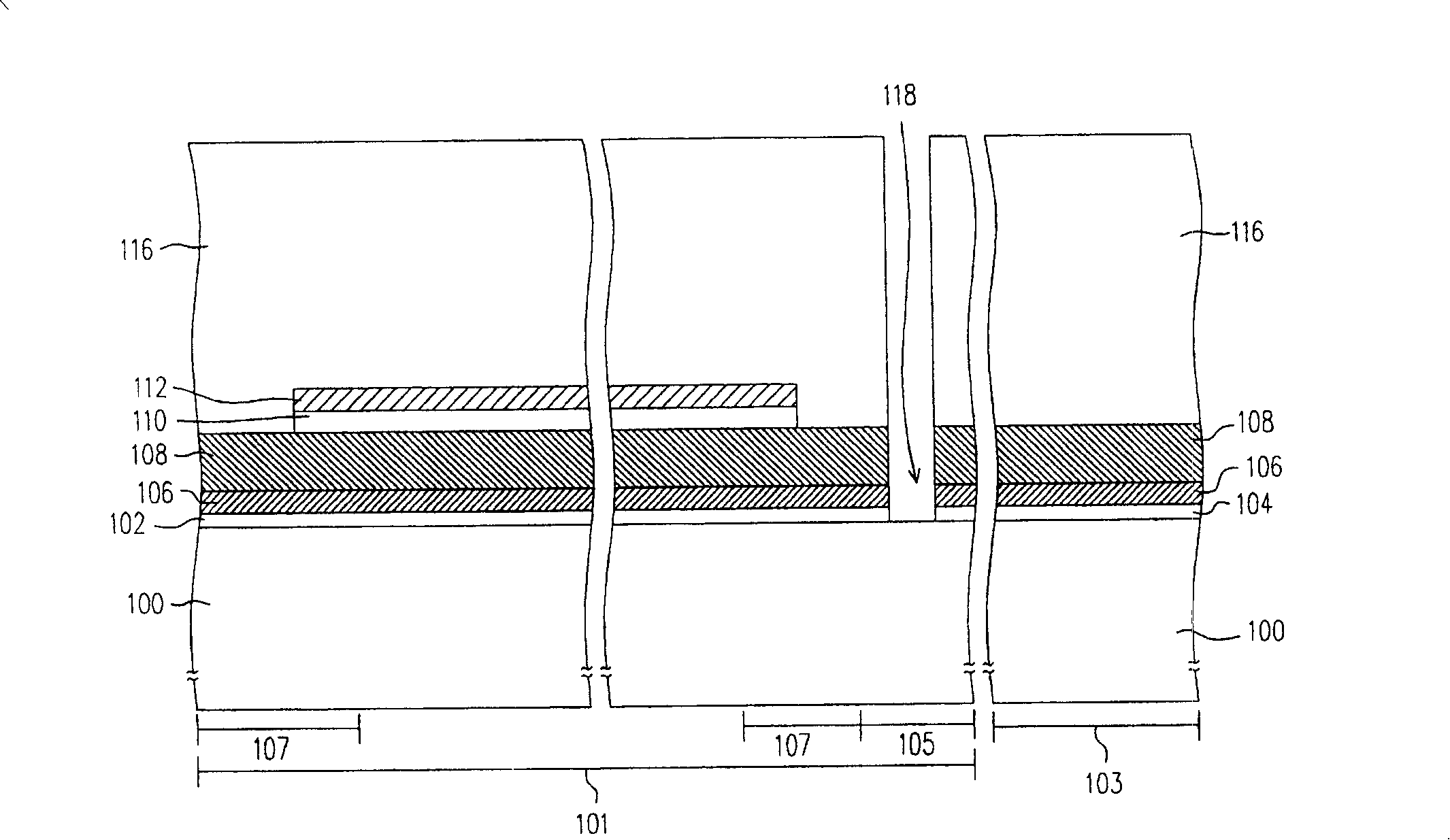

[0050] Figure 1A to Figure 1F It is a sectional view of the fabrication process of the non-volatile memory according to the embodiment of the present invention.

[0051] First, please refer to Figure 1A , a substrate 100 is provided, and the substrate 100 is, for example, a silicon substrate. The substrate 100 has a memory cell area 101 and a peripheral circuit area 103 . The memory cell region has a source line region 105 and a select gate region 107 .

[0052] Then, a tunnel dielectric layer 102 is formed on the substrate 100 in the memory cell area 101 , and a gate dielectric layer 104 is formed on the substrate 100 in the peripheral circuit area 103 . The materials of the tunneling dielectric layer 102 and the gate dielectric layer 104 are, for example, silicon oxide, and the methods for forming them are well known to those skilled in the art, and will not be repeated here. In addition, the thicknesses of the tunneling dielectric layer 102 and the gate dielectric laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com