Multi-speed interconnected reliability testing structure

一种测试结构、互连结构的技术,应用在半导体/固态器件测试/测量、电气元件、电固体器件等方向,能够解决影响芯片功能、电路短路等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

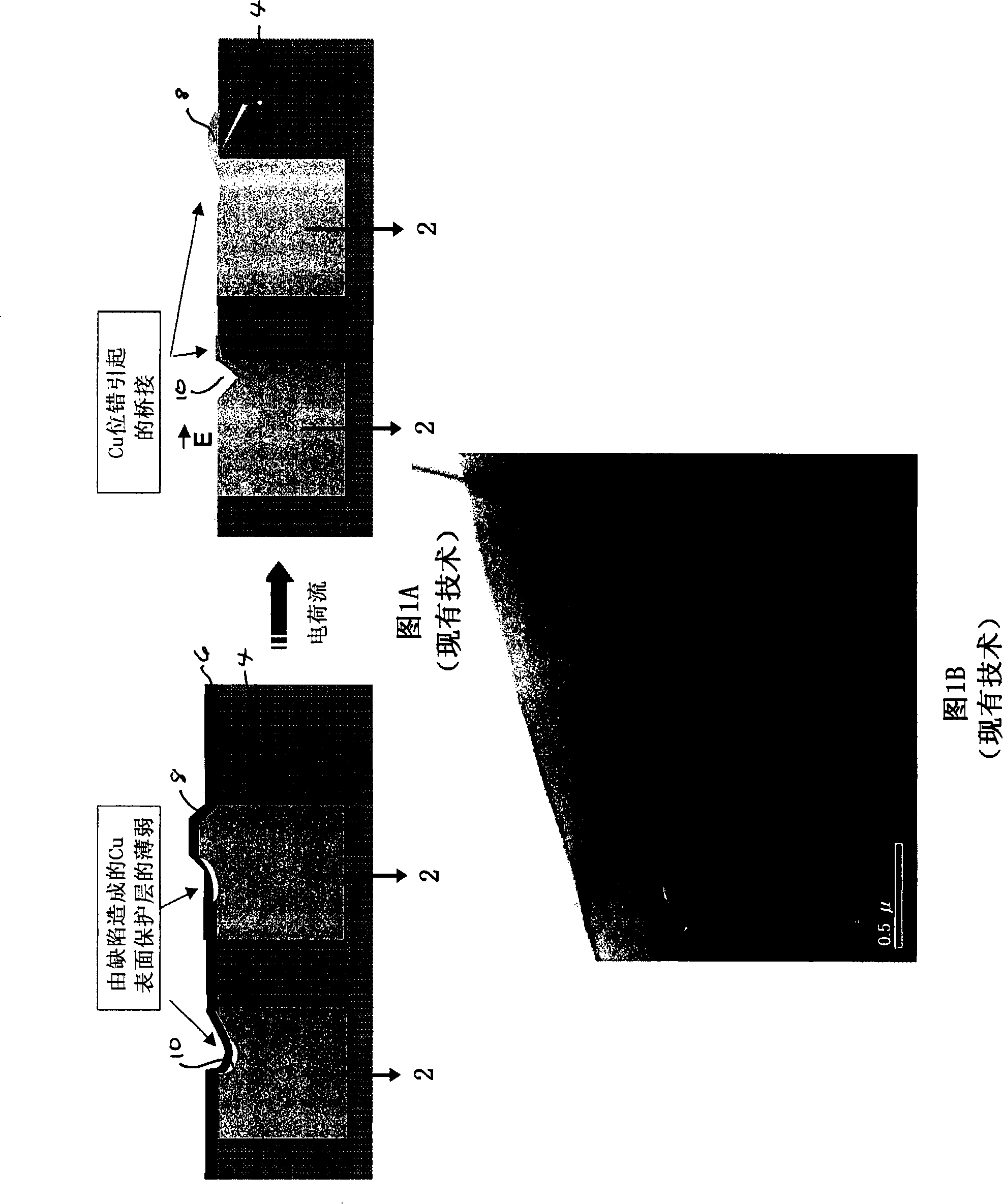

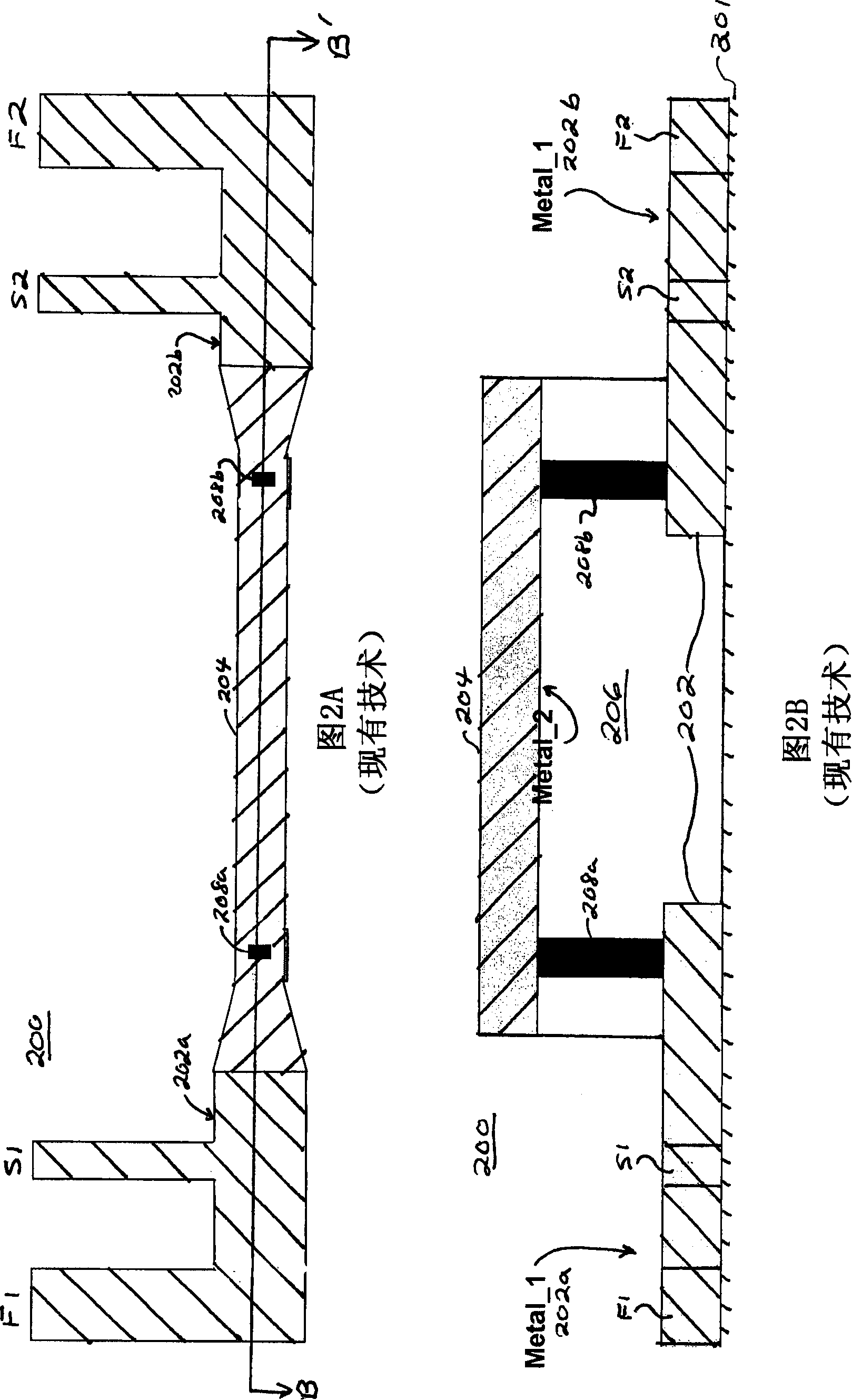

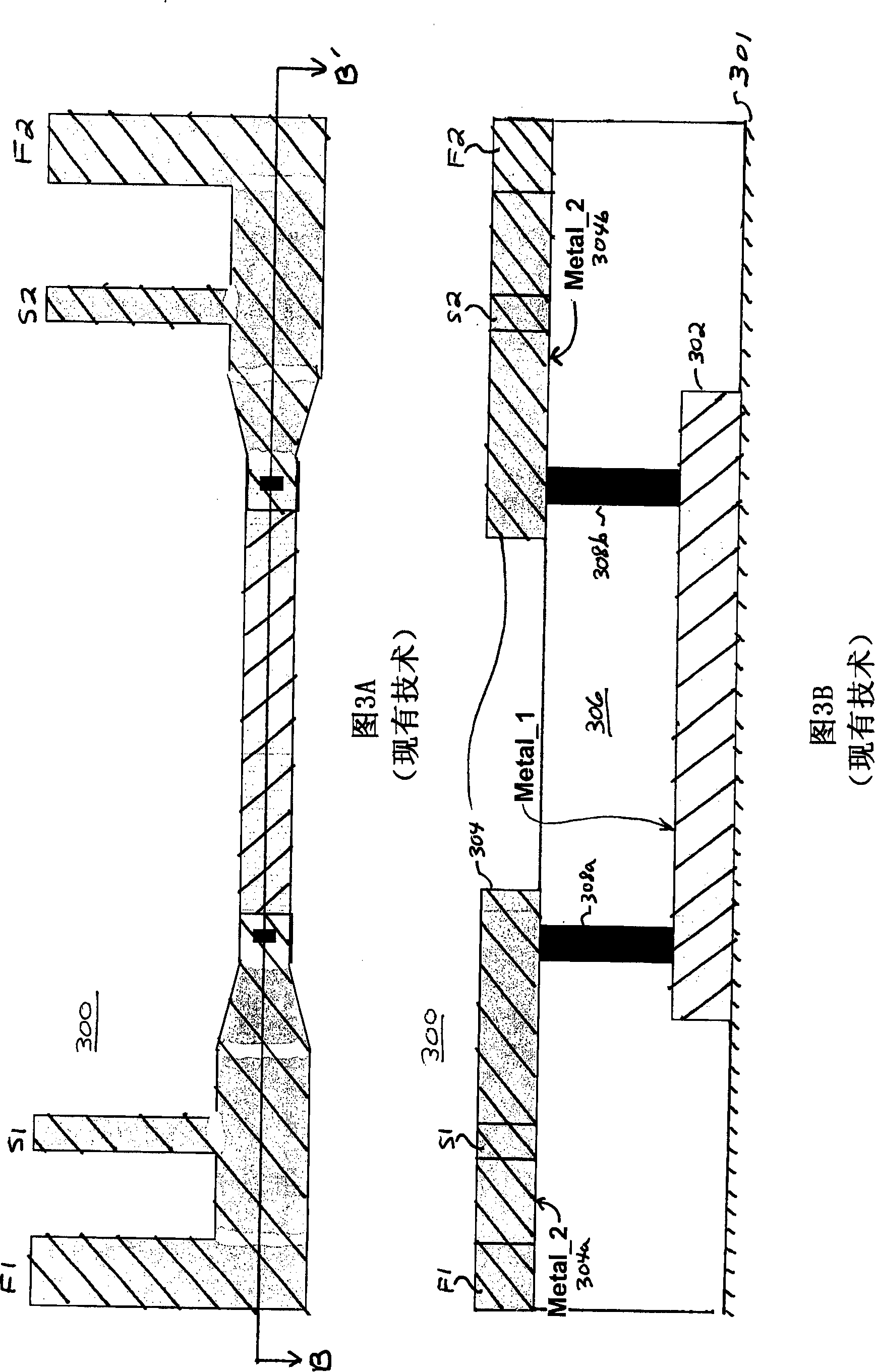

[0030] Typically, testing of metallized interconnect structures involves the investigation of different failure mechanisms. For example, the point of failure may be near the top or bottom of a via connecting different metal lines, or it may be along the metal line itself.

[0031] The entire content of the following document is hereby incorporated by reference: EIA / JEDEC Standard EIA / JESD61 (April 1997) entitled "Isothermal Electromigration Test Procedure". This document describes standardized tests for estimating electromigration (EM) along metallized feature lines of interconnect structures. In particular, the test describes a standardized test for estimating electromigration (EM) along metallized feature lines of an interconnect structure. In particular, the test is used to identify electromigration that occurs along relatively long metal lines, eg, pieces of 200 μm or greater, and typically 800 μm or greater in length. The EM test is performed by applying a loading volta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com