Simultaneous core testing in multi-core integrated circuits

A technology of integrated circuits and logic cores, applied in the field of structural testing of multi-core integrated circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

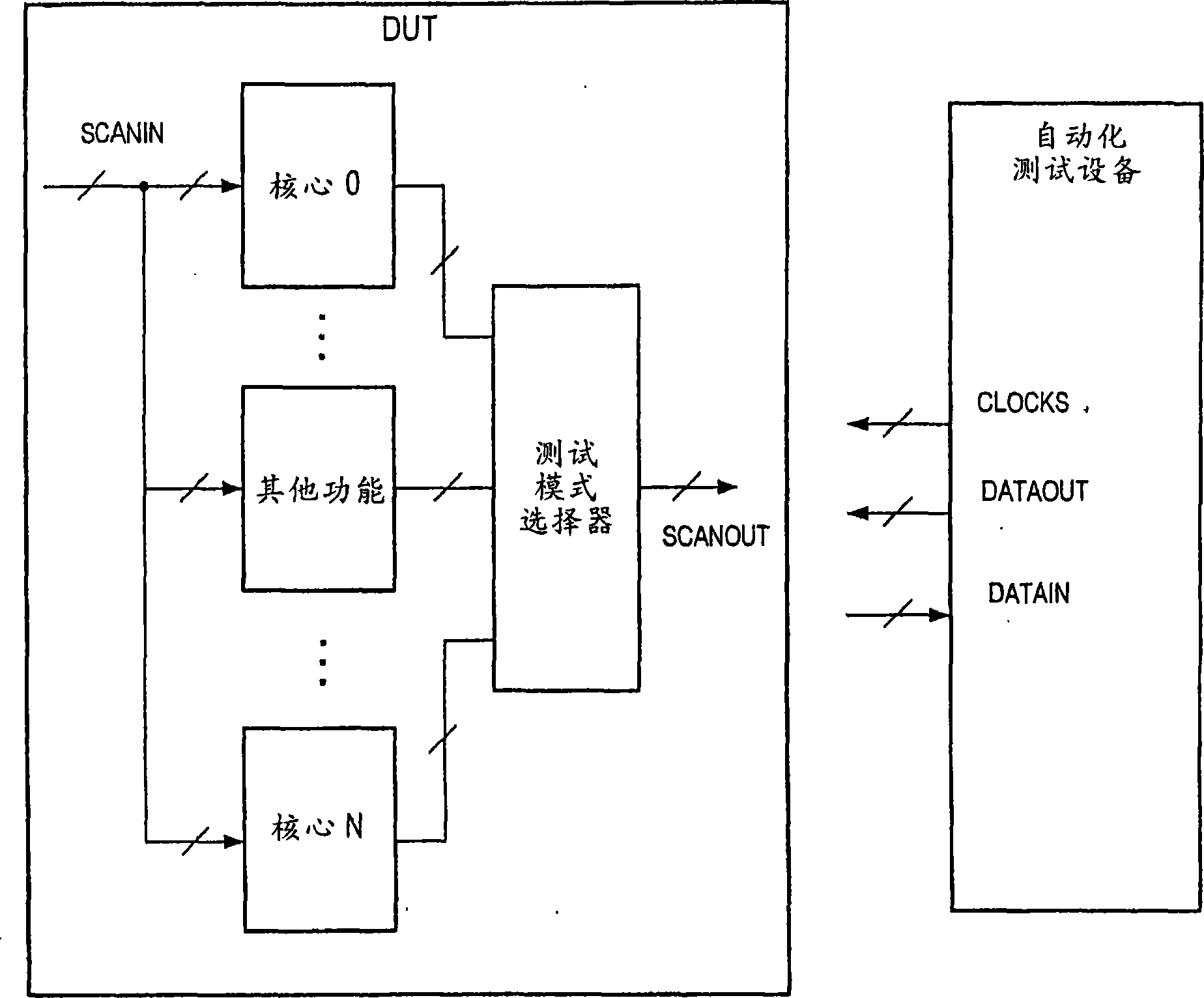

[0032] FIG. 1 illustrates a system for testing an integrated circuit including multiple logic cores, according to one embodiment. In one embodiment, a device under test (DUT) may be a chip multiprocessor, and cores 0 to N may be the same. The DUT may also include other circuits not included in the core. For example, the DUT may include bridging and / or memory control functions that allow the core to access common memory or other resources. In some cases, the base core that is duplicated in the multi-core DUT can be included in a previously developed single core IC. For example, a microprocessor chip containing only core 0 and the other functional blocks of the DUT may have been previously fabricated and tested using the automated test equipment (ATE) shown in FIG. 1 . In this case, it is best to use the same ATE that was used to test the previous IC, and test the DUT with minimal changes to hardware and software and without increasing test pattern size or test time.

[0033]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com