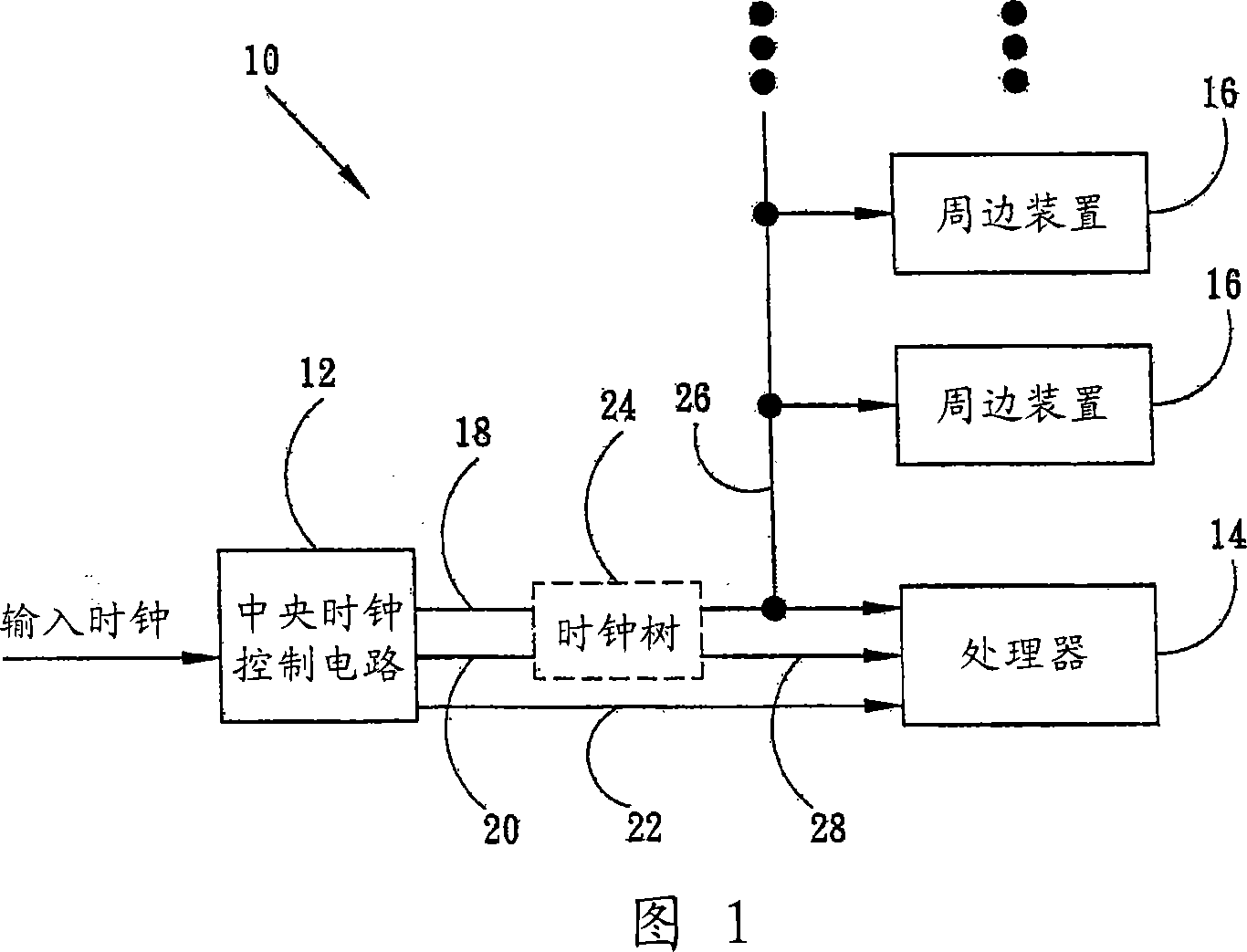

Dynamically synchronizing a processor clock with the leading edge of a bus clock

A clock system and clock technology, applied in the direction of generating/distributing signals, can solve the problems of incorrect synchronization of bus and processor clock, misalignment of bus and processor clock, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0088] Some embodiments of the present invention are described in detail as follows. However, the invention can be practiced broadly in other embodiments than those described in detail, and the scope of the invention should not be limited except by the claims hereof. Furthermore, in this specification, different parts of each component are not drawn to scale. Certain dimensions have been exaggerated compared to other relevant dimensions to provide a clearer description and understanding of the invention.

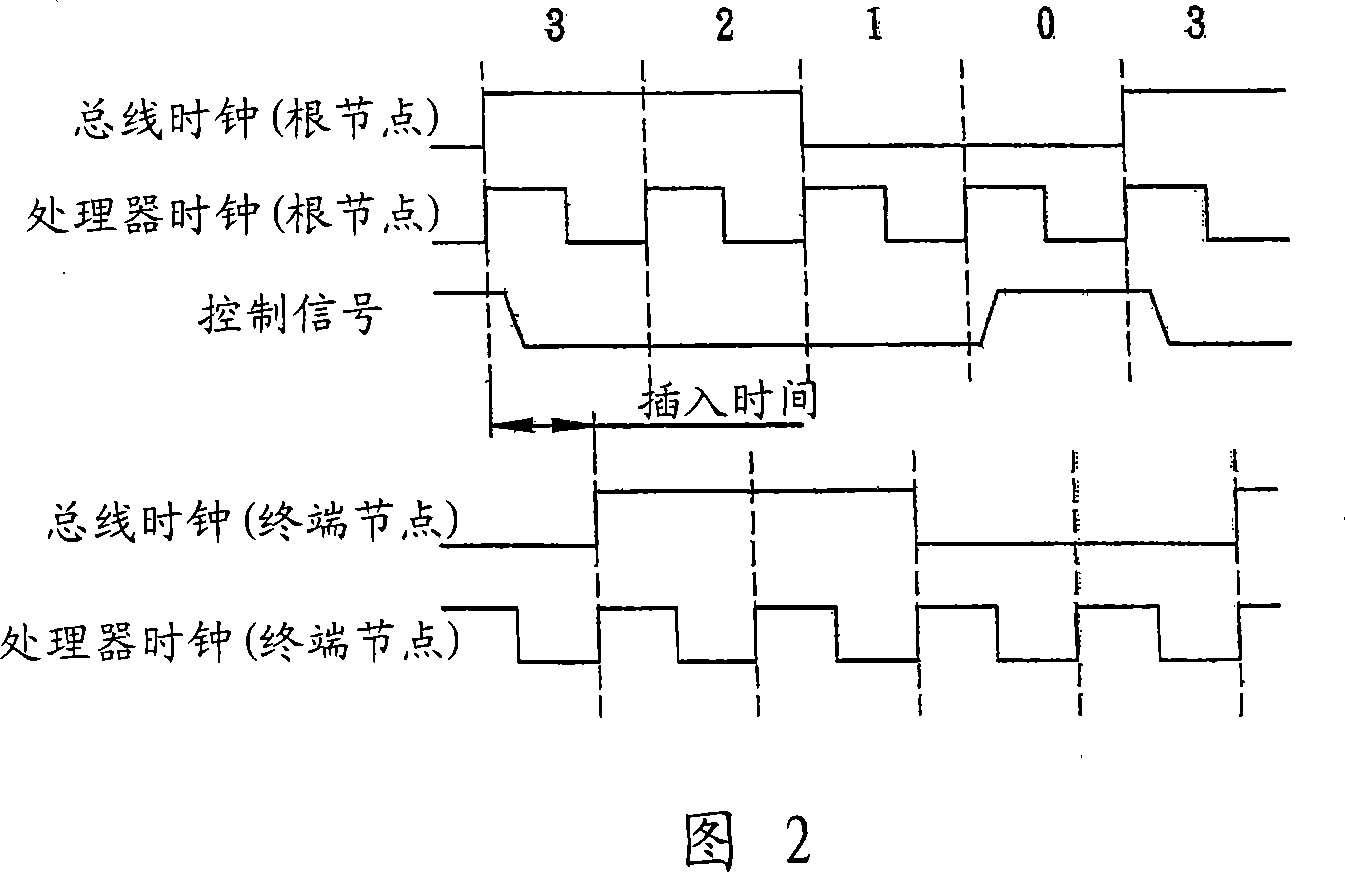

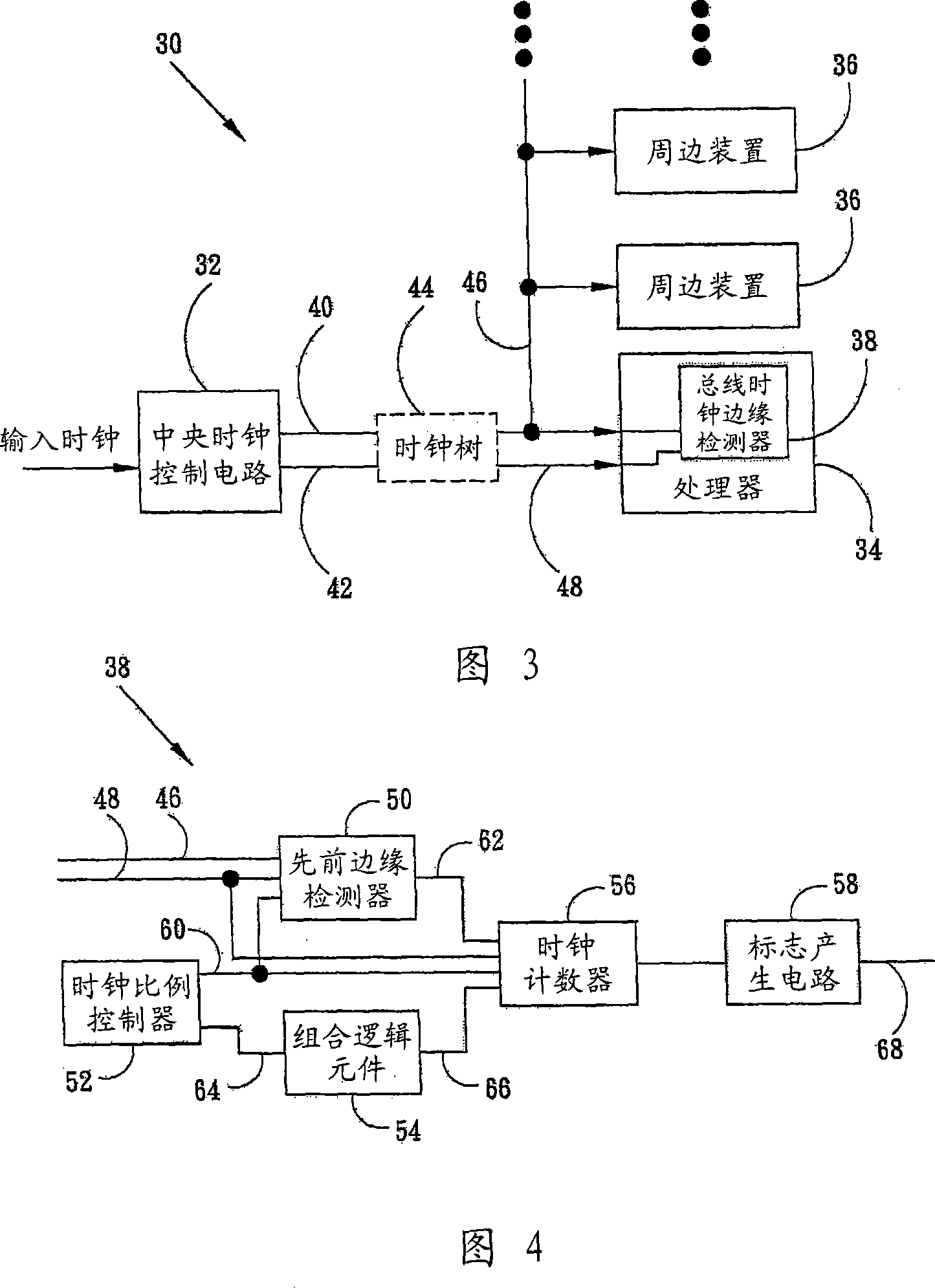

[0089] Since the central clock control circuit is used to generate control signals in the prior art, the bus clock inserted into the time delay and the processor clock signal cannot be aligned, resulting in timing problems, and chip designers need to manually design delay circuits to remove control signal error. The present invention uses a logic circuit to generate a flag signal, which is similar in concept to a control signal; however, the flag signal is only locally gen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com