PMOS tube production method capable of improving instability of negative temperature

A technology of instability and manufacturing method, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of large Vt drift, PMOS negative temperature instability, Idsat increase, etc., to reduce the threshold voltage Drift, the effect of alleviating the effect of negative temperature instability, reducing the effect of saturation leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

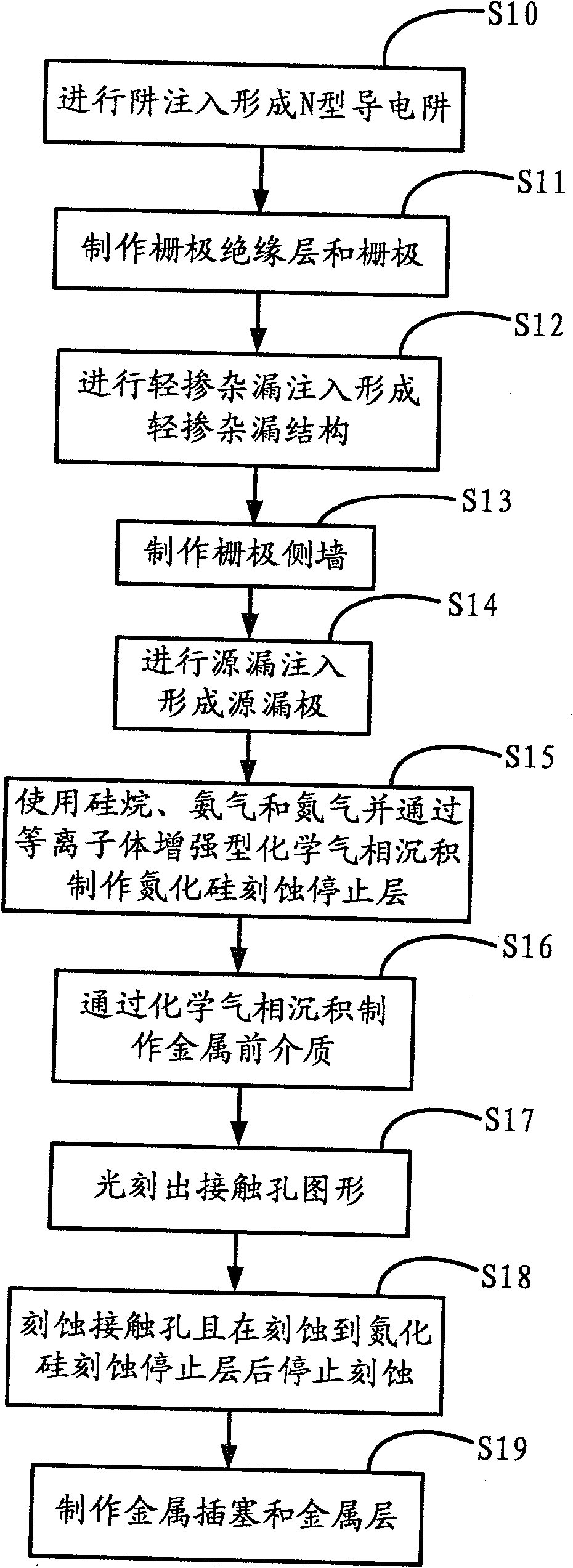

[0013] The following will further describe in detail the manufacturing method of the PMOS transistor capable of improving the negative temperature instability of the present invention.

[0014] see figure 1 According to the PMOS transistor manufacturing method capable of improving the negative temperature instability of the present invention, the first step S10 is to perform well implantation to form an N-type conductive well. In this embodiment, an N-type conductive well is formed by phosphorus doping.

[0015] Then continue to step S11 , forming a gate insulating layer and a gate, wherein the gate insulating layer is silicon oxynitride or silicon oxide, and the gate is a polysilicon gate.

[0016] Then continue to step S12, perform lightly doped drain implantation to form a lightly doped drain structure. In this embodiment, the lightly doped impurity is boron fluoride.

[0017] Then continue to step S13 , making gate sidewalls.

[0018] Then continue to step S14, perform...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com