Integrated circuit with memory cells comprising a programmable resistor and method for addressing memory cells comprising a programmable resistor

A technology for memory cells and integrated circuits, which is applied in the field of integrated circuits containing memory cells including programmable resistors and for addressing memory cells including programmable resistors, can solve problems such as inability to provide sufficient power and the like

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

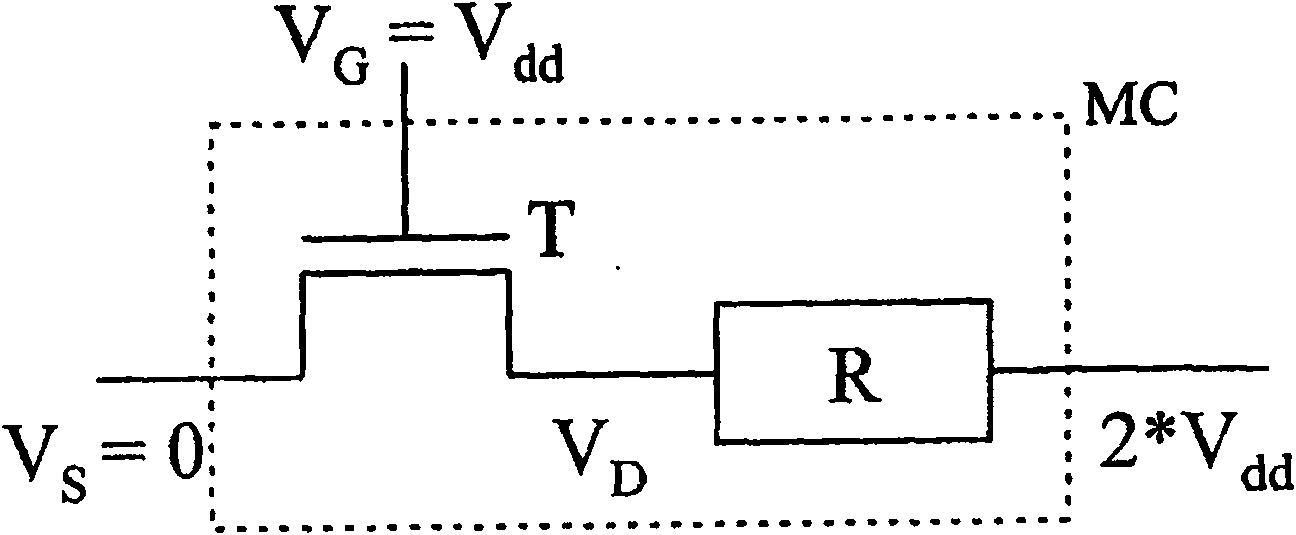

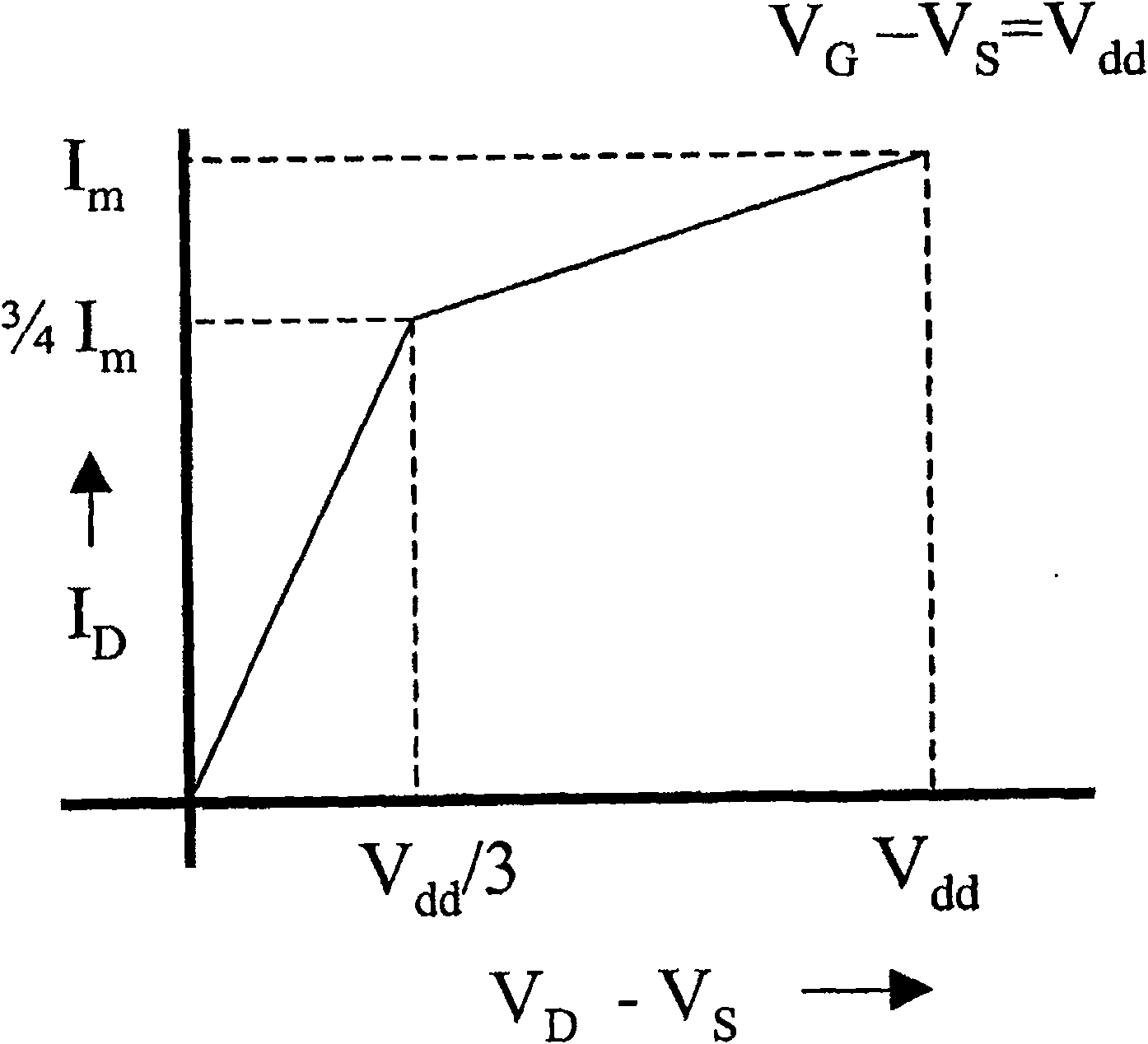

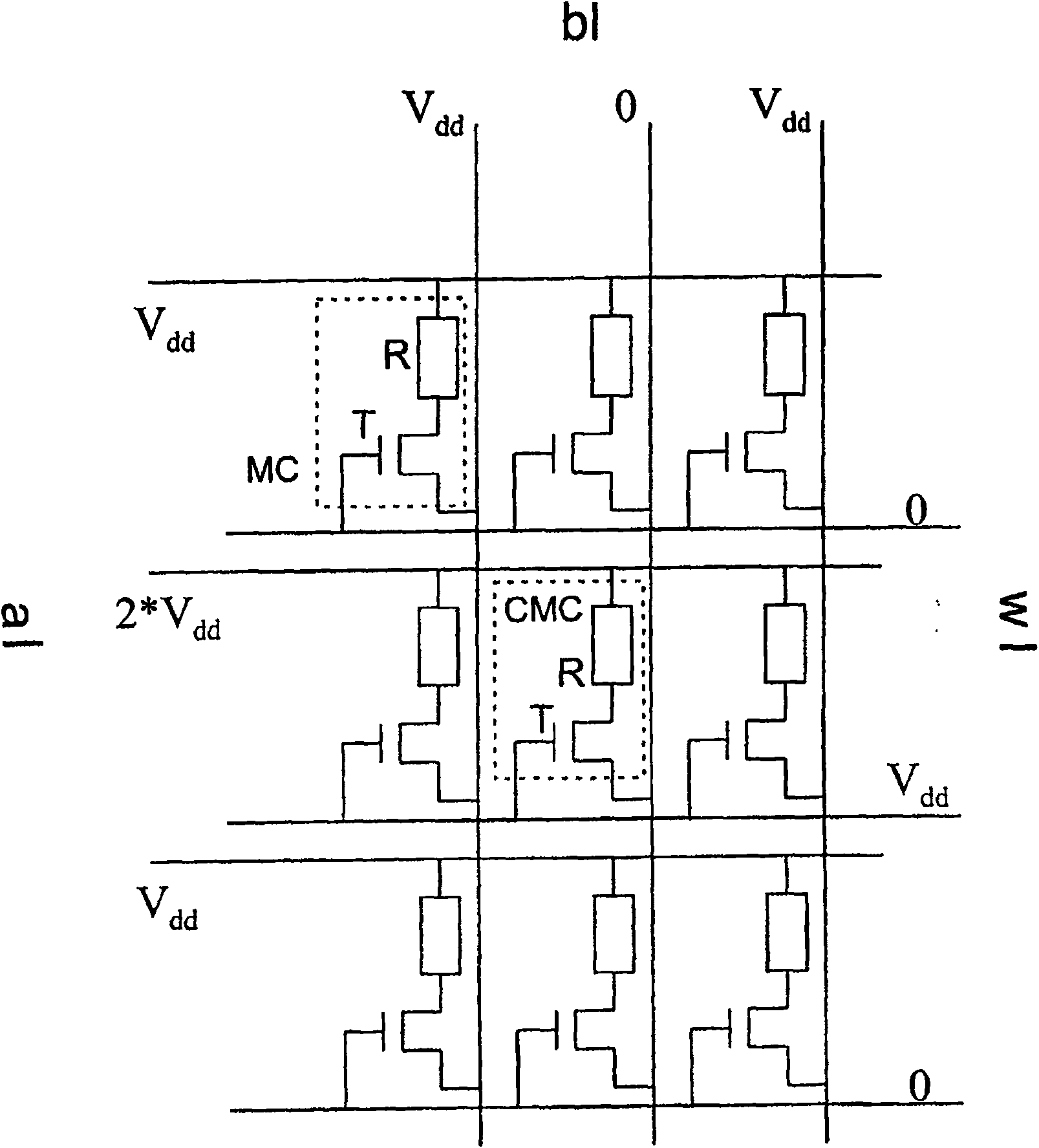

[0032] figure 1 A circuit diagram of a basic phase change memory cell according to a first embodiment of the present invention is shown. If the selected value of the programmable resistor R is such that V d -V s about V dd / 3, then the best power dissipation of the programmable resistor can be obtained in the memory cell.

[0033] therefore,

[0034] P opt m *V dd

[0035] P opt =3 / 4*I m *2 / 3*V dd =1 / 2*I m *V dd

[0036] R opt =(2 / 3V dd ) / (3 / 4*I m )=8 / 9*(V dd / I m )

[0037] P opt ≤ I m *V dd

[0038] One side of the programmable phase change resistor R is connected to the drain terminal of the NMOS transistor T, 2*V dd The voltage is applied to the other side of the programmable phase change resistor R. When the source terminal is connected to the common ground V s =0, the voltage V dd Applied to the drain terminal of the NMOS transistor T.

[0039] The value of resistor R must be designed so that the following equation holds:

[0040] V D =2*V ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com