Stress sensor chip based on SOI

A stress sensor and insulator technology, applied in semiconductor devices, semiconductor/solid state device testing/measurement, application of piezoresistive material property force measurement, etc. , to achieve the effect of high temperature reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The invention proposes a stress sensor chip based on a silicon-on-insulator chip. The working principle of the present invention will be described below in conjunction with the accompanying drawings.

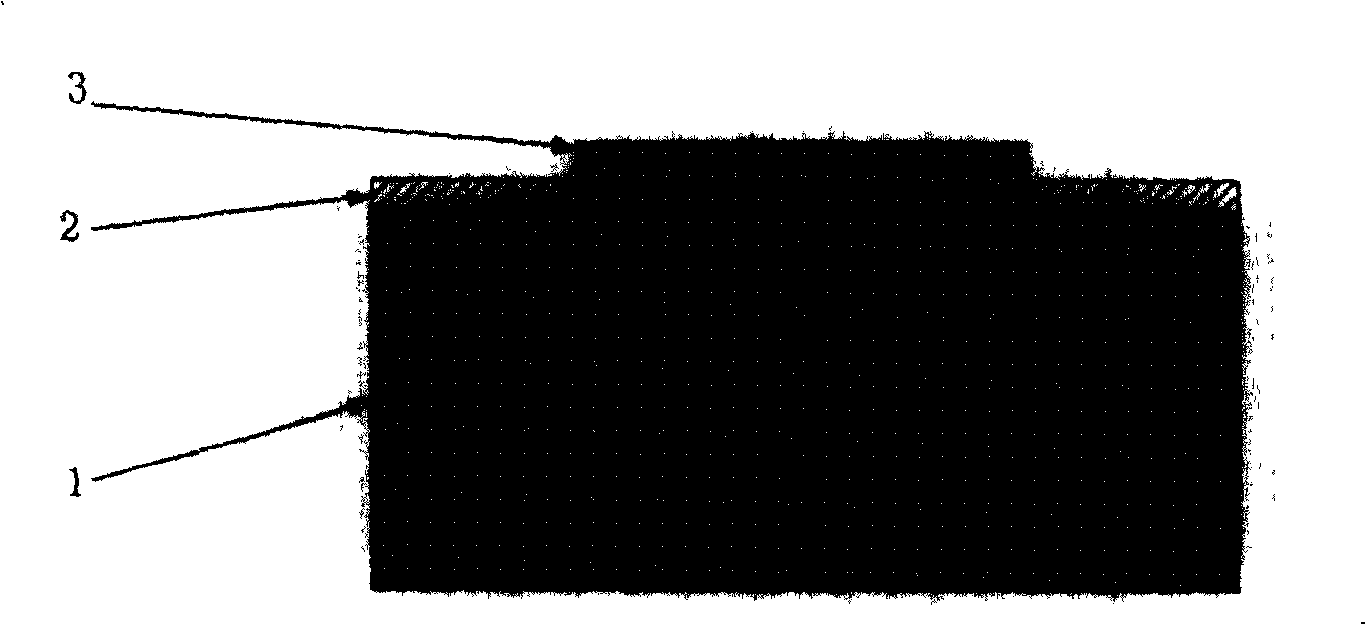

[0017] figure 1 A schematic diagram of the structure of a stress sensor chip on an SOI silicon wafer is shown. exist figure 1 In this method, a silicon dioxide insulating layer 2 is formed on a silicon substrate 1, and a stress-sensitive element layer 3 is formed on the silicon dioxide insulating layer 2. The SOI silicon chip realizes the insulation between the stress-sensitive element layer and the substrate by oxidizing the insulating layer 2, and can still maintain insulation even at high temperatures, ensuring the reliability of the sensor chip. The reverse-biased PN junction realizes the insulation between the stress-sensitive element layer and the substrate, and when the temperature rises, the increase of reverse-bias leakage current will affect the performance o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com