STI channel filling method

A technology of trench filling and trenching, which is applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of reducing the performance of the STI insulating isolation filling layer, aggravating the leakage current of the insulating isolation layer, and improper content ratio, etc., to achieve The effect of increasing the amount, eliminating silicon particles, and increasing the content ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

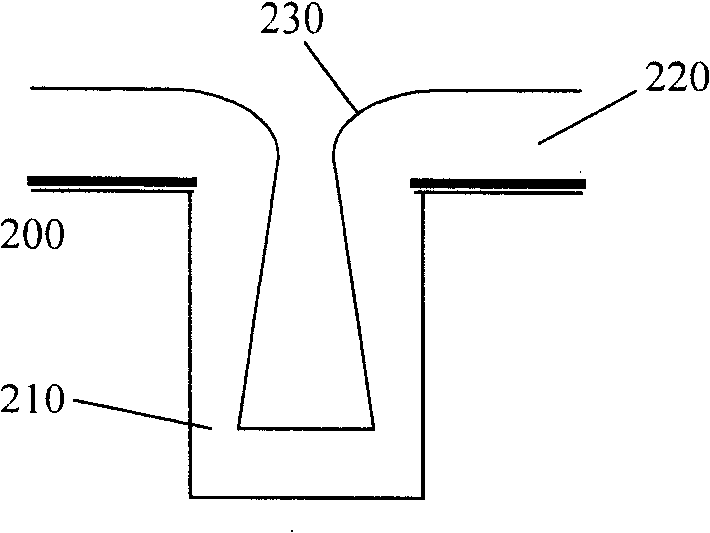

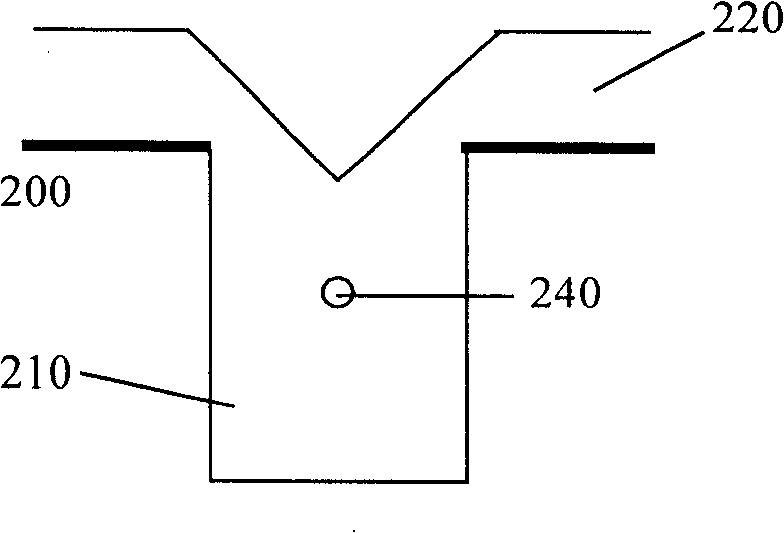

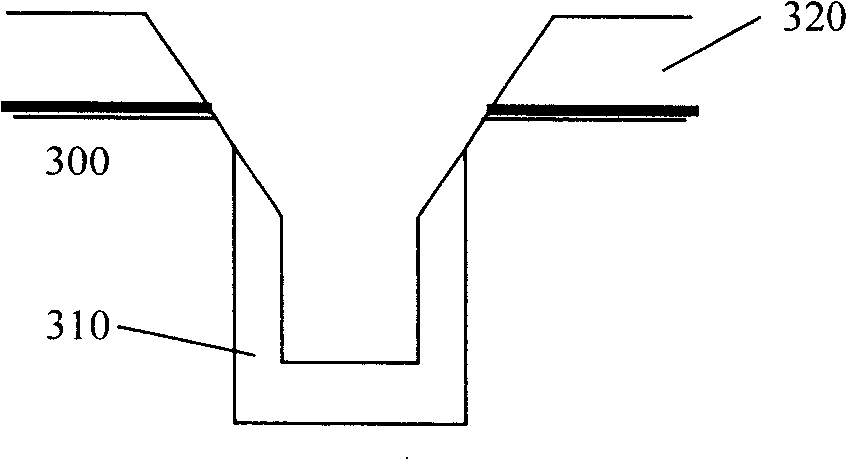

[0034] The STI trench isolation structure is used in integrated circuits as an isolation technology between components. The components are separated by etched trenches to insulate them from each other. The silicon oxide filling method for STI trenches of the present invention firstly provides a substrate in a reaction chamber, and forms trenches on the substrate by using processes such as masking, photolithography and etching. For the shallow trench isolation structure of the semiconductor process below 0.13 μm, the aspect ratio of the trench is generally greater than 3; and for the shallow trench isolation structure of the 90nm semiconductor process, the aspect ratio of the trench is Will reach 4 or higher, and the width is about 130-140nm.

[0035] The function of the STI trench is to isolate and insulate the components between multipl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com