Etch singulated semiconductor package

a semiconductor and singulated technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical equipment, etc., can solve the problems of premature wear of the costly saw singulated blade, cutting through copper with the saw blade, and the lead of the separated leadframes being burrowed, etc., to achieve the effect of reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

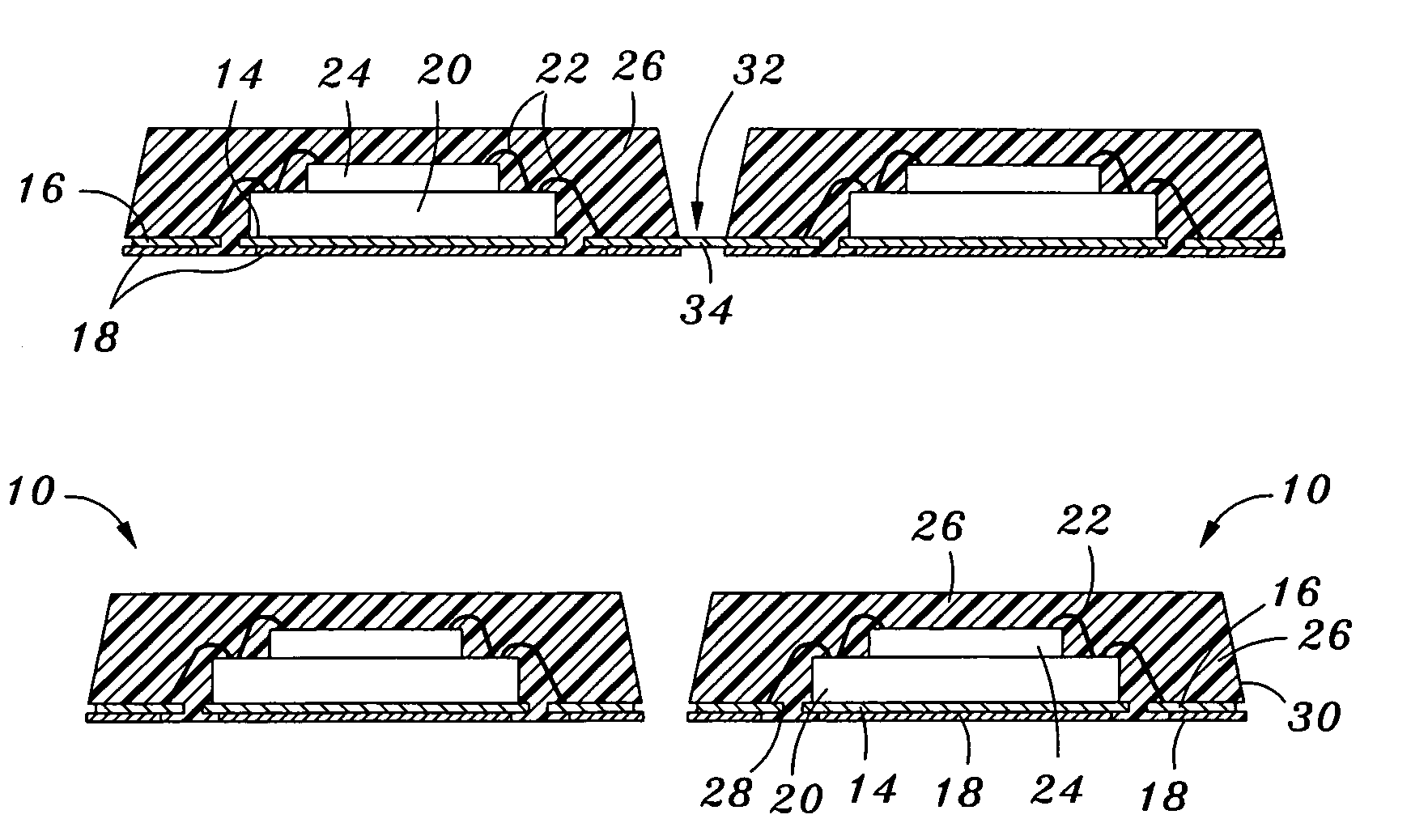

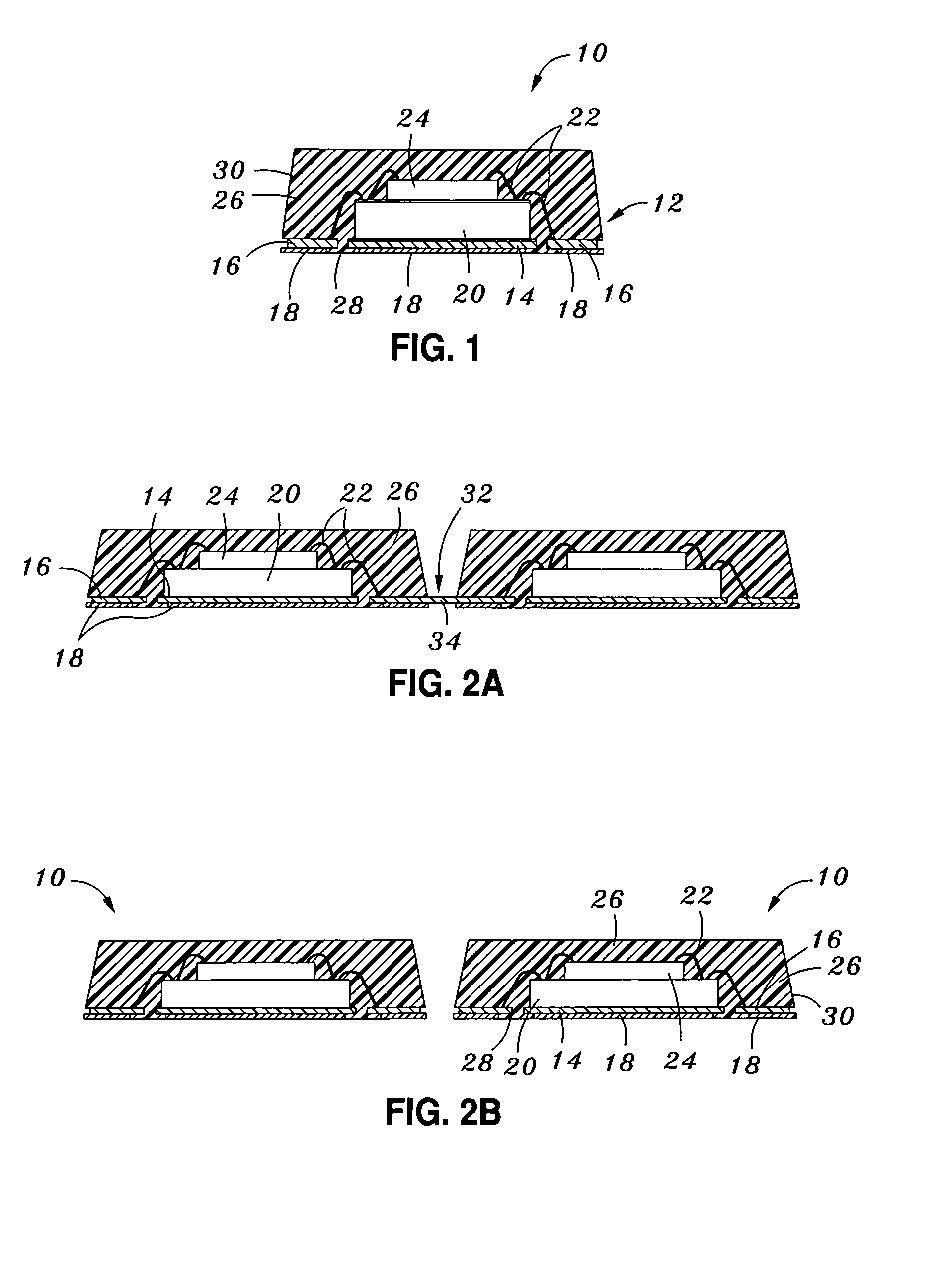

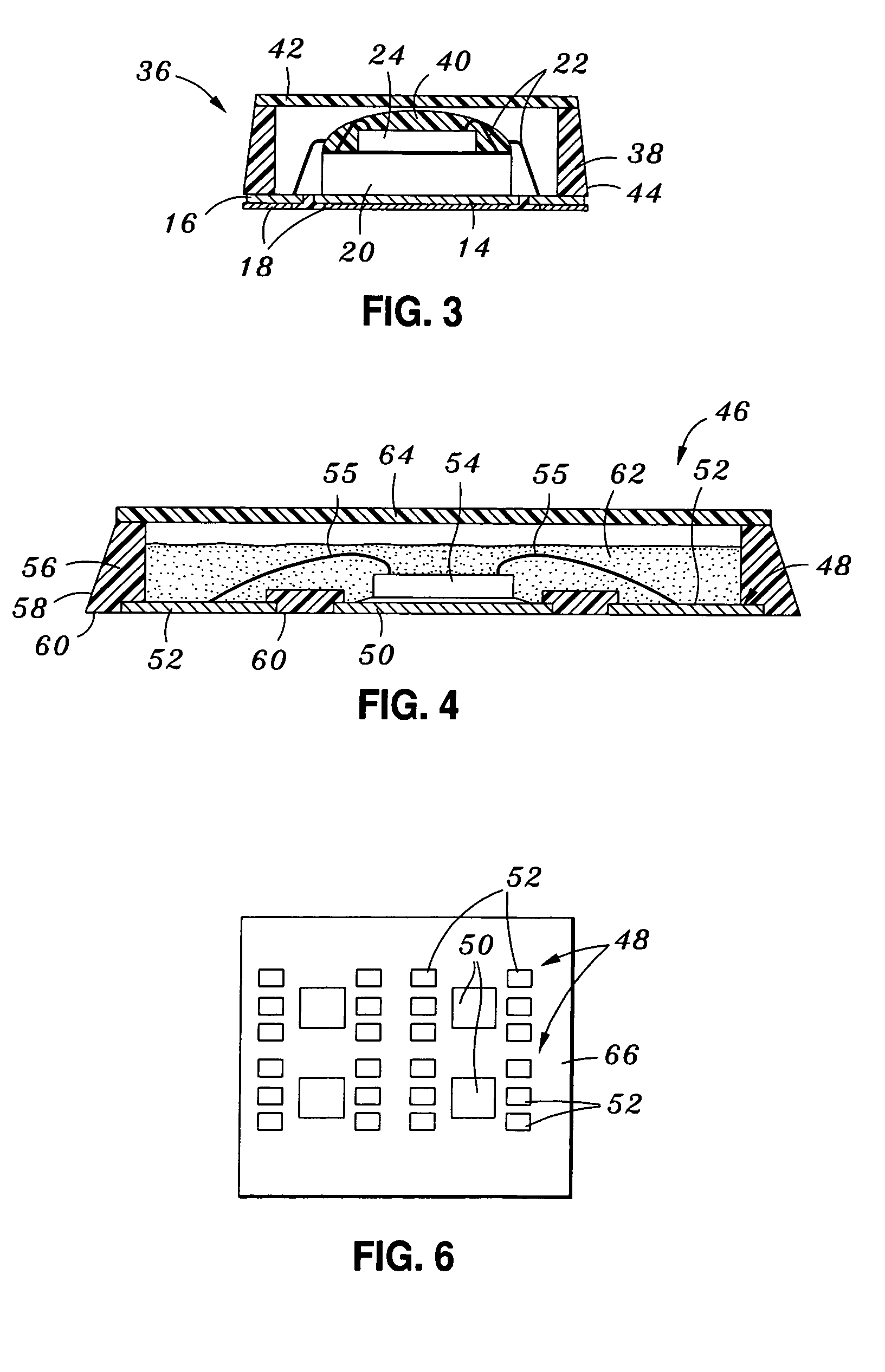

[0021]Referring now to the drawings where the showings are for purposes of illustrating various embodiments of the present invention only, and not for purposes of limiting the same, FIG. 1 illustrates a semiconductor package 10 constructed in accordance with one embodiment of the present invention. The semiconductor package 10 comprises a leadframe 12 which is preferably fabricated from a conductive metal material (e.g., copper). The leadframe 12 includes a die pad 14 which has a generally quadrangular (e.g., square, rectangular) configuration and defines opposed, generally planar top and bottom surfaces. In addition to the die pad 14, the leadframe 12 includes a plurality of leads 16. The leads 16 are typically segregated into multiple sets, with the leads 16 of each set extending along and in spaced relation to a respective one of the peripheral edge segments defined by the die pad 14. In this regard, the leadframe 12 of the semiconductor package 10 may be provided with one or mor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com