Method of forming a finfet structure

a technology of non-planar transistors and fin structures, which is applied in the direction of basic electric elements, electrical apparatus, and semiconductor devices, can solve the problems of poor cd uniformity of the fin structure of the fin structure of the fin structure of the fin-fet, and the current planar fets no longer meet the requirements of the products, so as to improve the quality of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014]To provide a better understanding of the present invention, preferred embodiments will be made in detail. The preferred embodiments of the present invention are illustrated in the accompanying drawings with numbered elements.

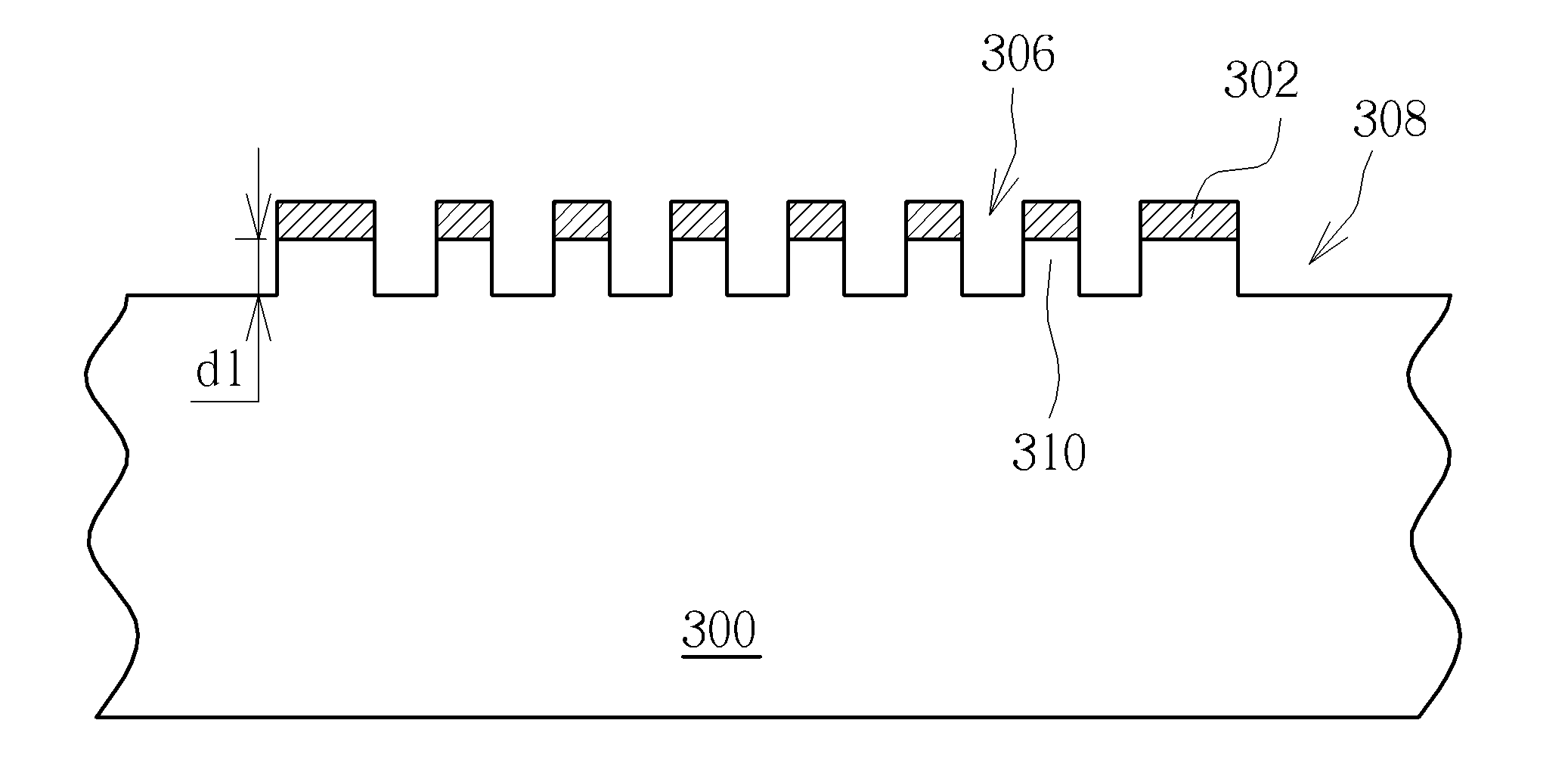

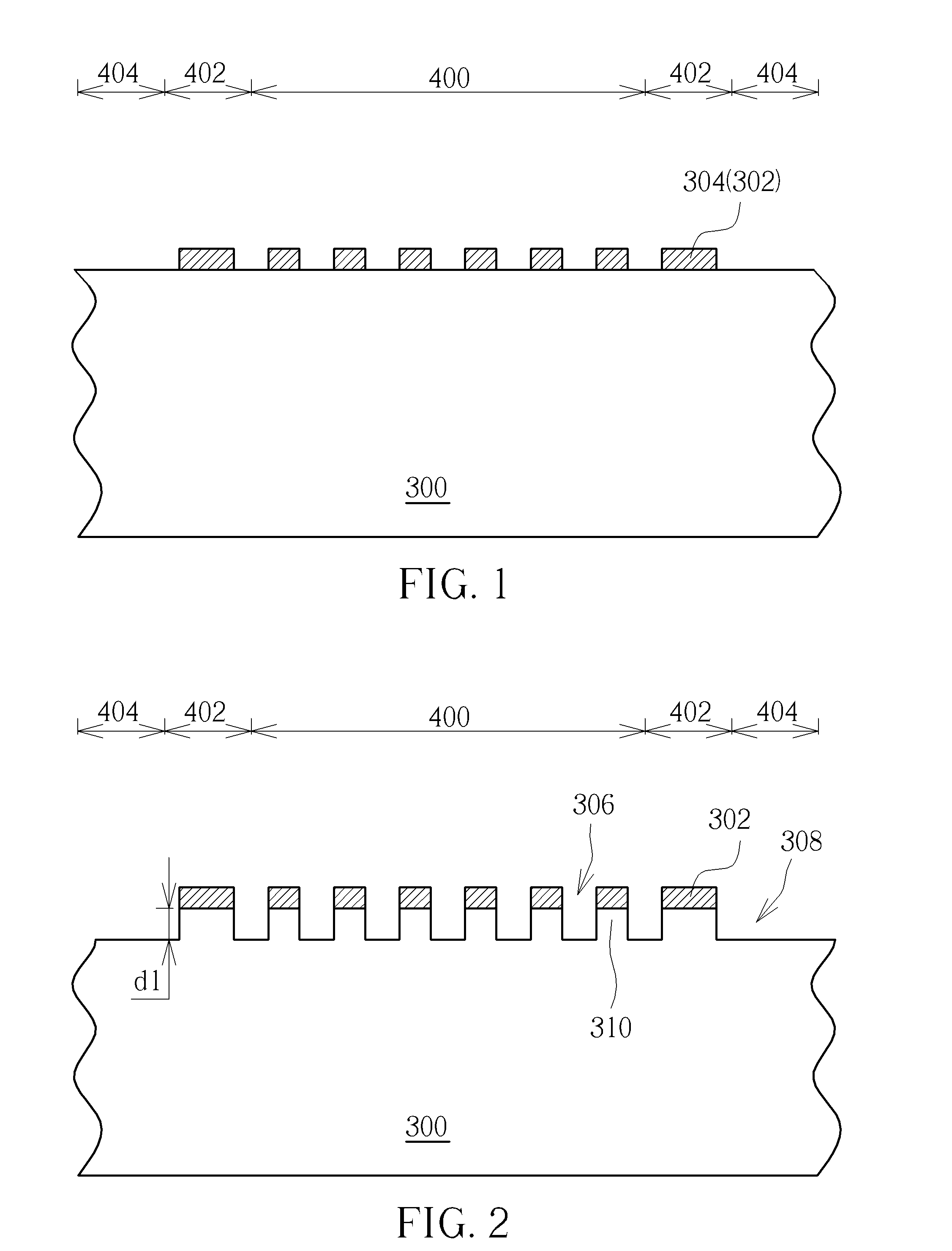

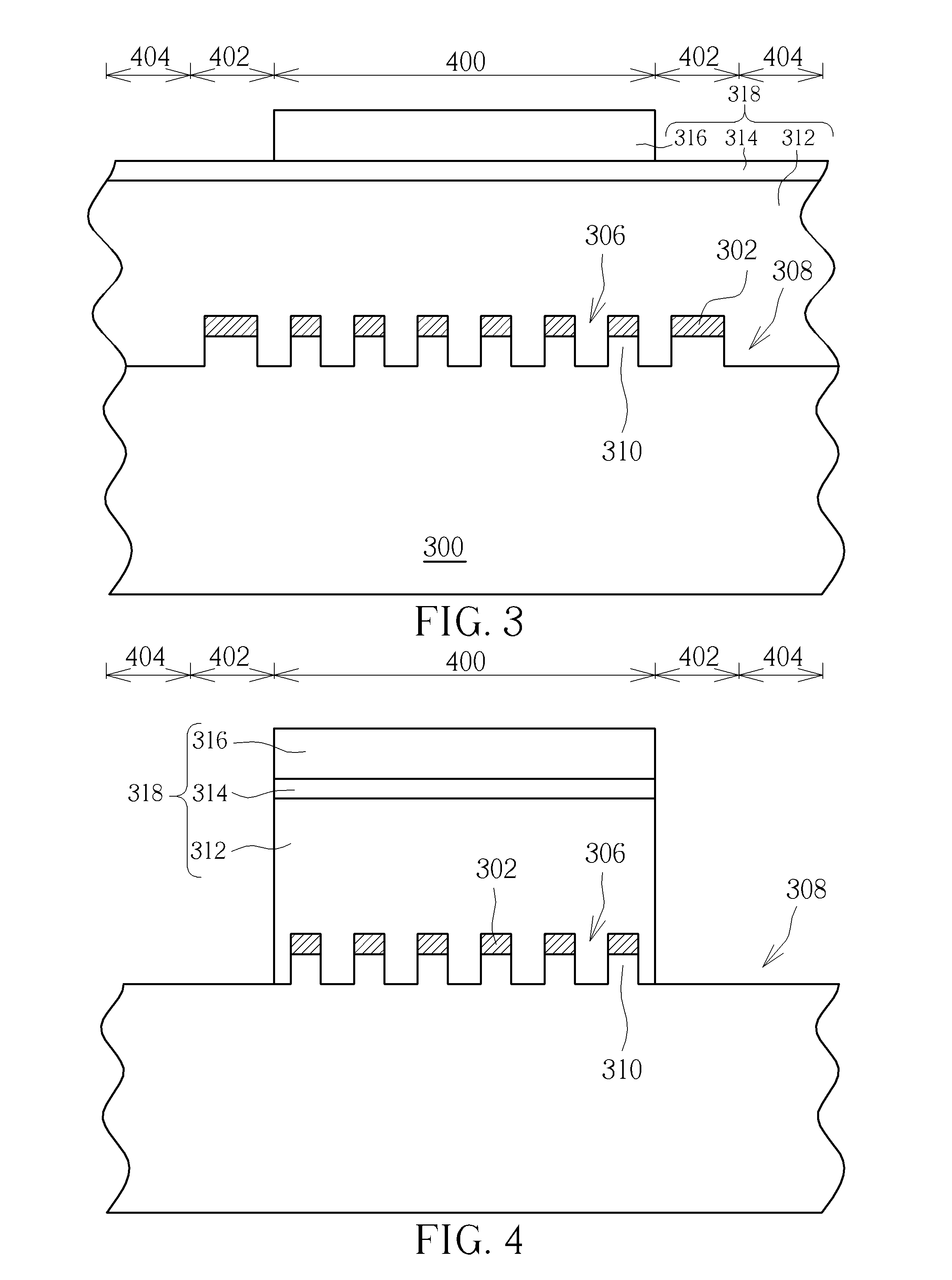

[0015]Please refer to FIG. 1 to FIG. 8, which are schematic diagrams of the fabrication method of a non-planar FET according to the first embodiment in the present invention. As shown in FIG. 1, a substrate 300 is provided. In one embodiment, the substrate 300 can be a silicon substrate, an epitaxial silicon substrate, a silicon germanium substrate or a silicon carbide substrate, but is not limited thereto. A first region 400, a second region 402 and a third region 404 are defined on the substrate 300. The second region 402 is disposed between the first region 400 and the third region 404 so that the second region 402 encompasses the first region 400, and the third region 404 encompasses both the first region 400 and the second region 402. A patterned mask...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com