System and method for managing timing margin in a hierarchical integrated circuit design process

a hierarchical integrated circuit and timing margin technology, applied in computer aided design, program control, instruments, etc., can solve the problems of increasing the investment of time and resources by the manufacturer to design and fabricate a digital logic device, increasing the possibility of a mistake or oversight on the part of the designer, and requiring greater complexity in digital logic design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

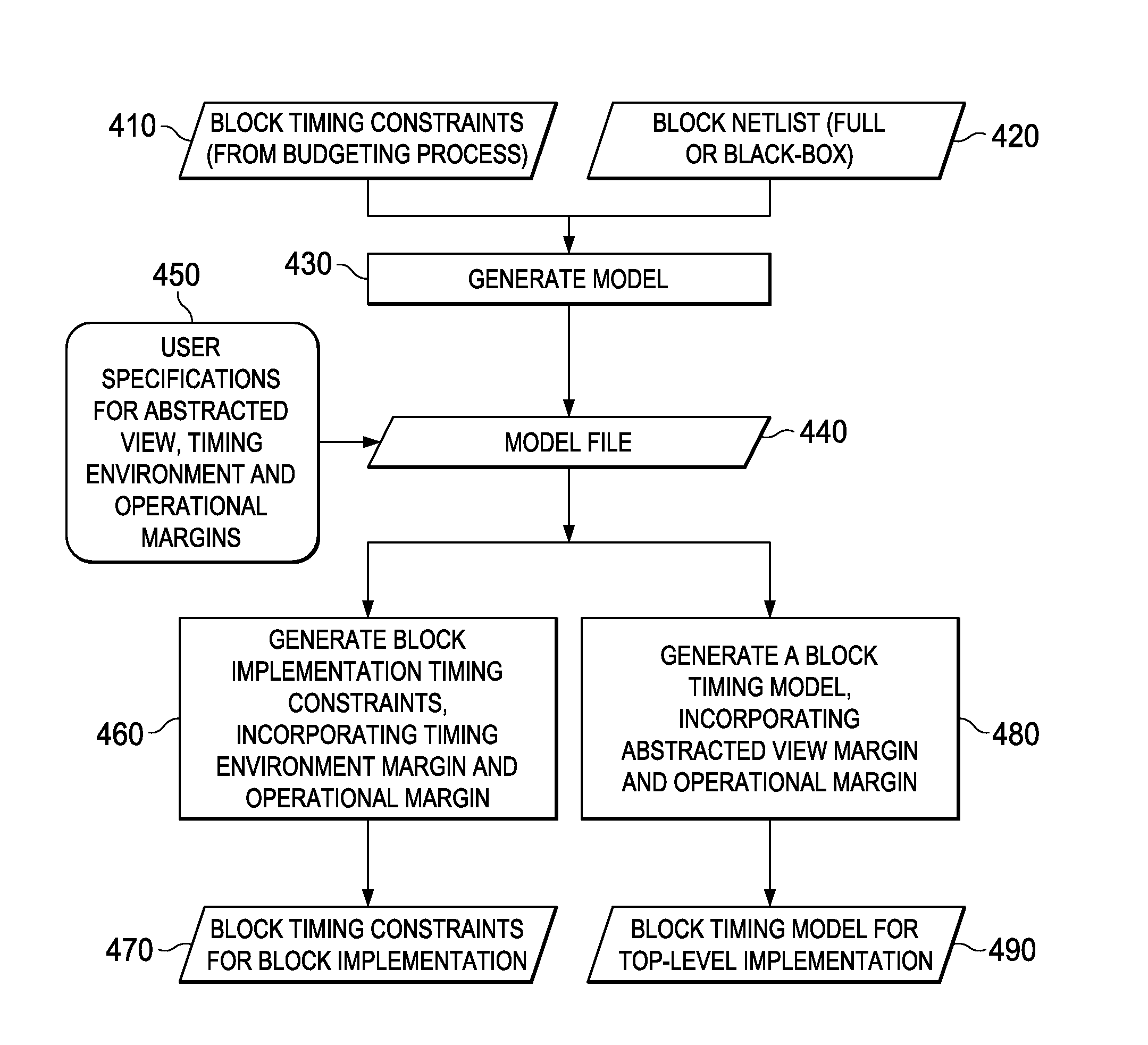

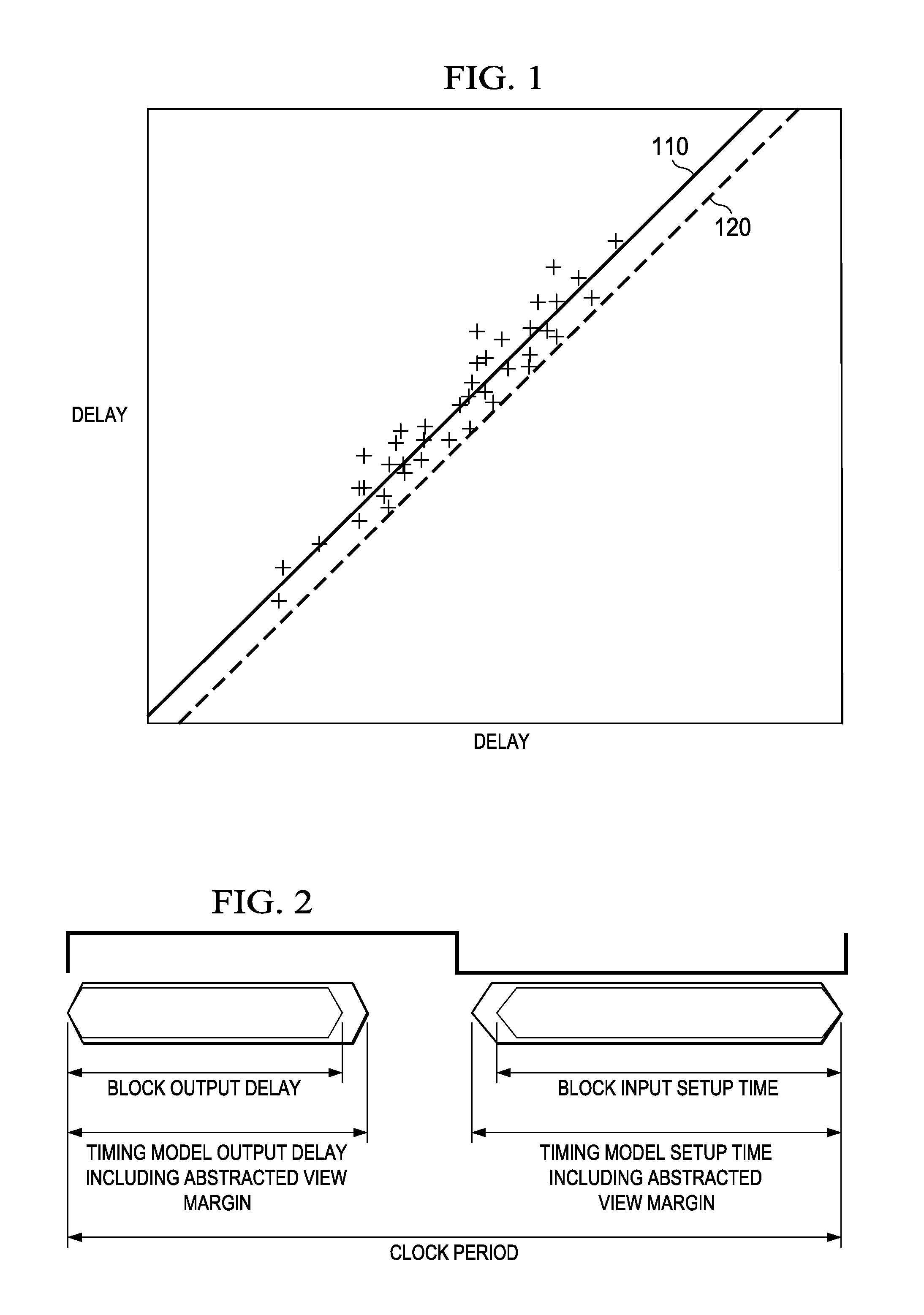

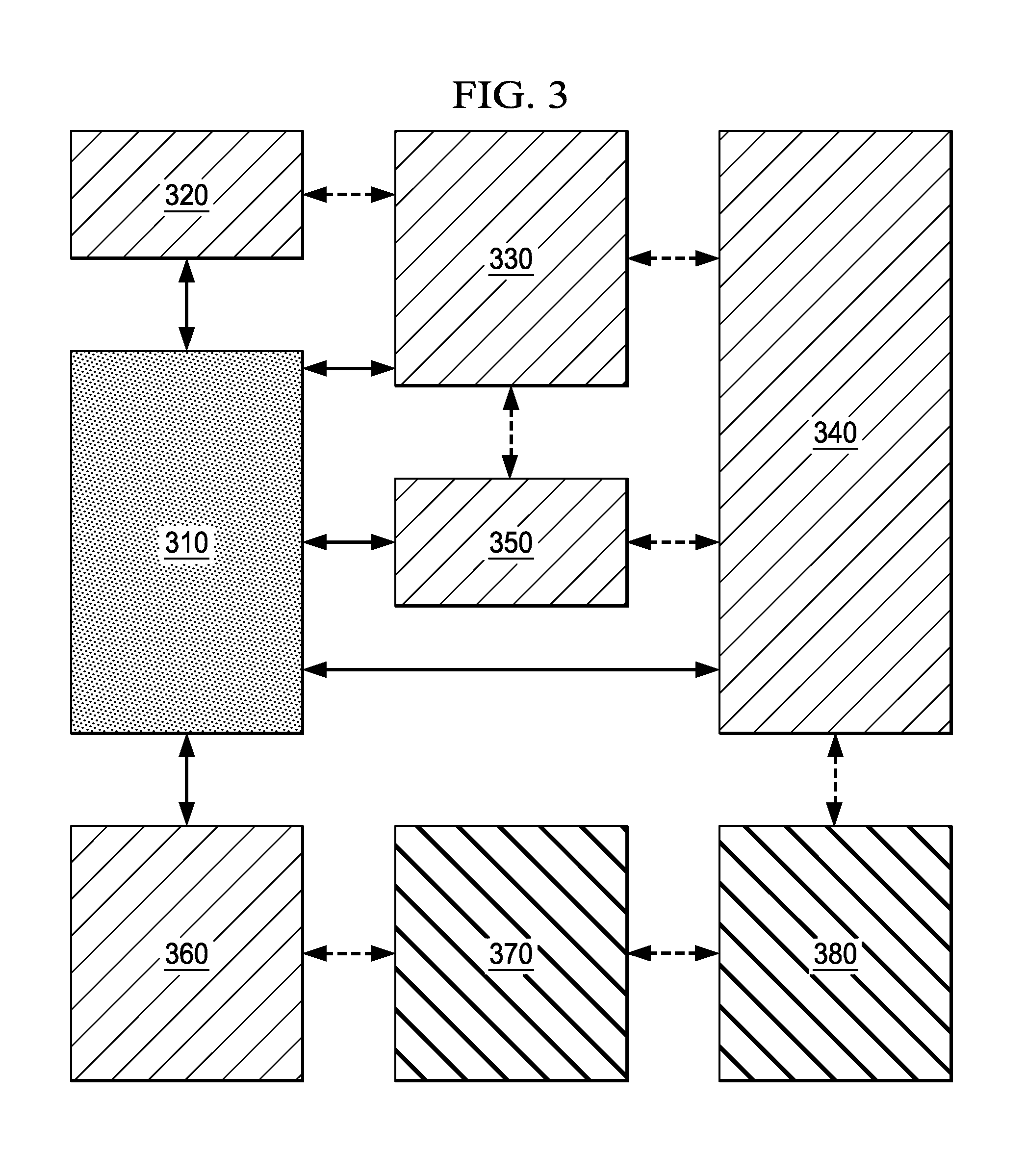

[0014]Performing timing signoff on a hierarchical design in a concurrent fashion requires representations or models of the timing of the lower level blocks before they are completed. The timing representations or models should be consistent with the constraints applied to the block designs to ensure predictable results when the hierarchical blocks and top level are integrated. In addition, electrical and operational factors should be taken into account in developing block constraints and timing models to allow timing to be closed without substantial surprises and redesign. Hierarchical design processes, or “flows,” in existing commercial tools are based on extracted timing models, and as such, do not allow for concurrent block and top-level execution. They also provide no means of accounting for issues that only appear at final timing closure.

[0015]Introduced herein are various embodiments of a system and method for managing timing margin in a hierarchical IC design flow. In general...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com