Layout method for soft-error hard electronics, and radiation hardened logic cell

a logic cell and hard electronics technology, applied in the field of soft-error hard electronics and radiation-hardened logic cells, can solve problems such as voltage pulses in circuits, and achieve the effect of reducing the effect of single event and protecting against soft errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

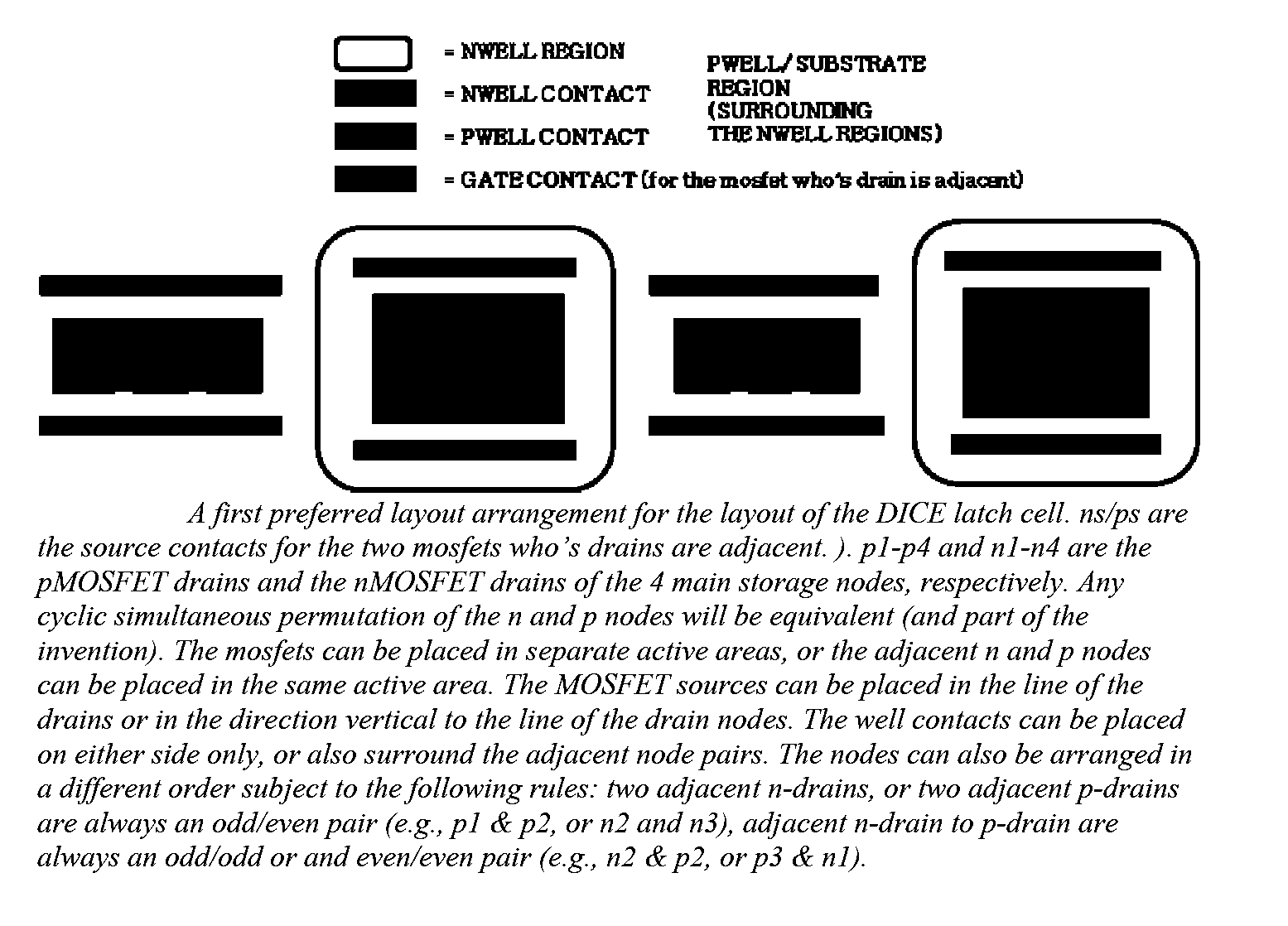

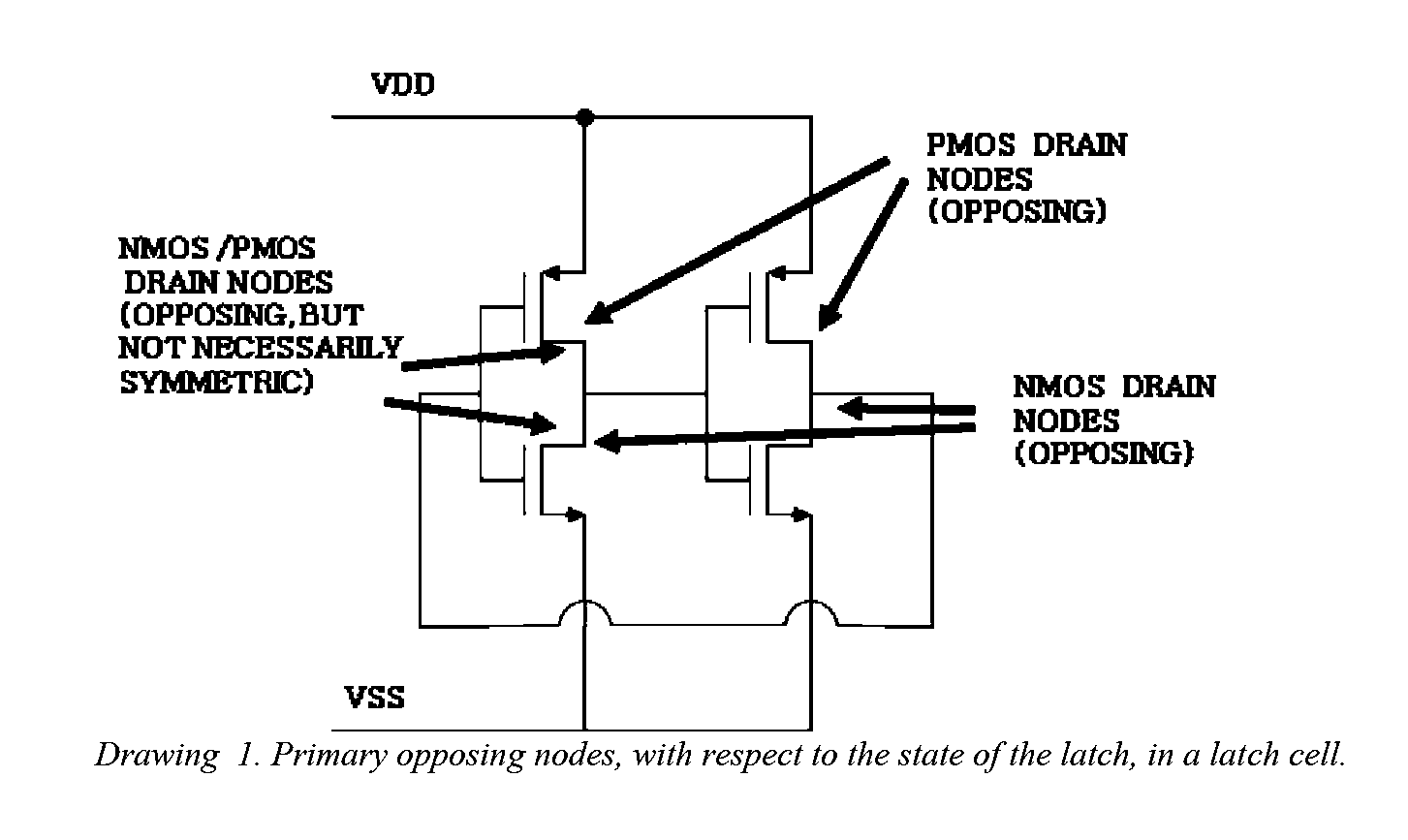

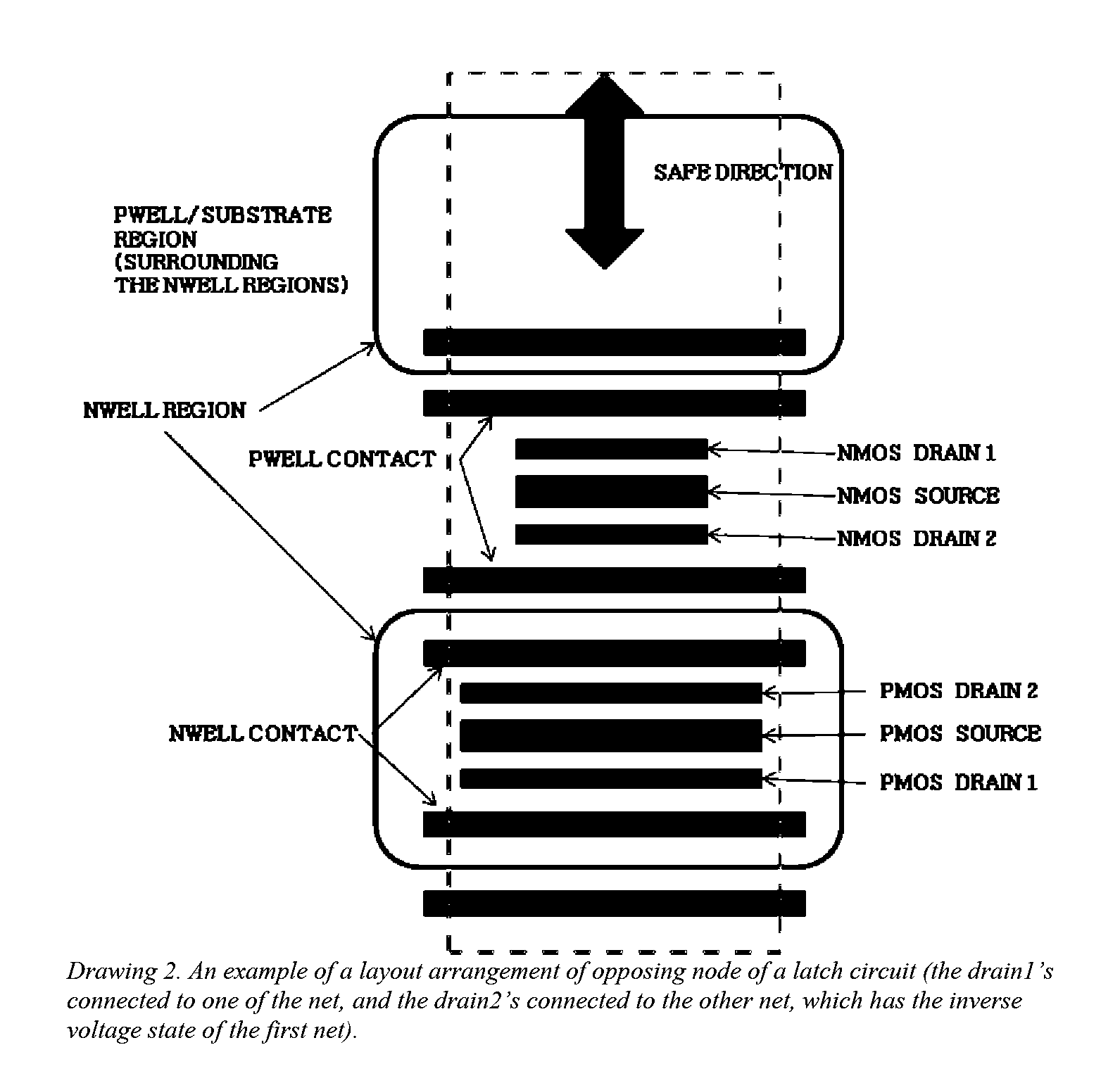

[0028]This invention comprises a unique new layout method, which takes advantage of the overall circuit response to a single event effect. It also includes specific circuit cells with layout, which have been constructed in accordance with the new layout method.

[0029]A radiation generated single event (soft-) error (SEE) occurs when the charge, generated in the semiconductor material by one or more (e.g. secondary) charged particles, is collected by contact areas. The contact areas are the low resistivity regions on, or in, the semiconductor substrate, which are connected to a net in the circuit, e.g., the source and drain areas in a MOSFET technology. A circuit net (or node) refers to a part of the circuit, connected by low resistivity regions (metal), which maintains a certain voltage value (referred to as the voltage state of the net) throughout its' extent. A net can be connected to any number of contact areas.

[0030]The charge collected by contact areas during a single event, lea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com