Method of forming a non-continuous conductive layer for laminated substrates

a technology of laminated substrates and non-continuous conductive layers, which is applied in the direction of printed circuit manufacturing, printed circuit stress/warp reduction, printed circuit aspects, etc., can solve the problems of continuous length of conductive materials, expansion and contraction of substrates, damage to equipment or render circuit boards useless, etc., to achieve the effect of eliminating continuous lengths of conductive materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The term “patterning” refers to one or more steps that result in the removal of selected portions of layers. The patterning process is also known by the names photomasking, masking, photolithography and microlithography. The term “circuit board” refers to a flat piece of insulating material, such as epoxy or phenolic resin, on which electrical components are mounted and interconnected.

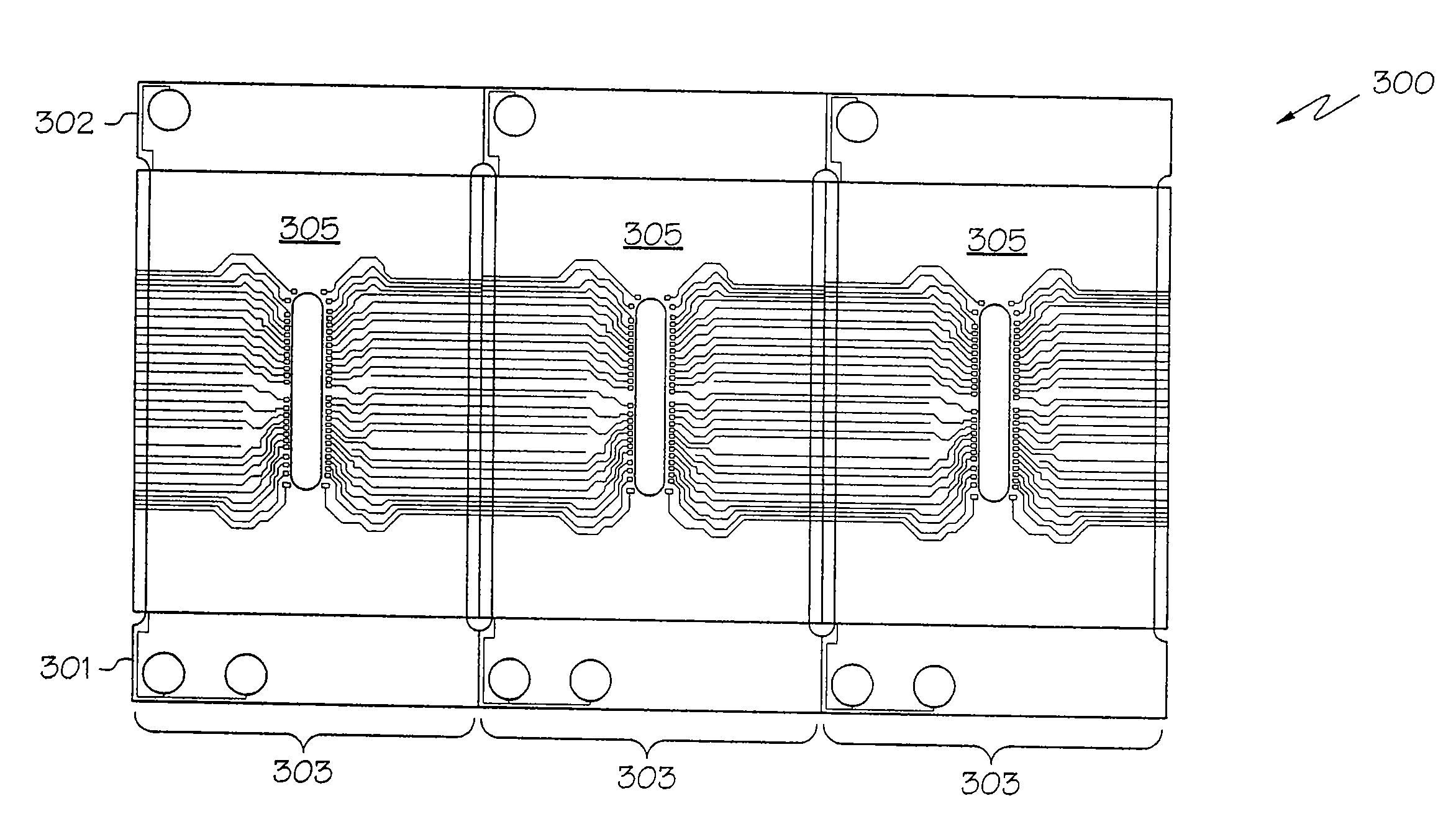

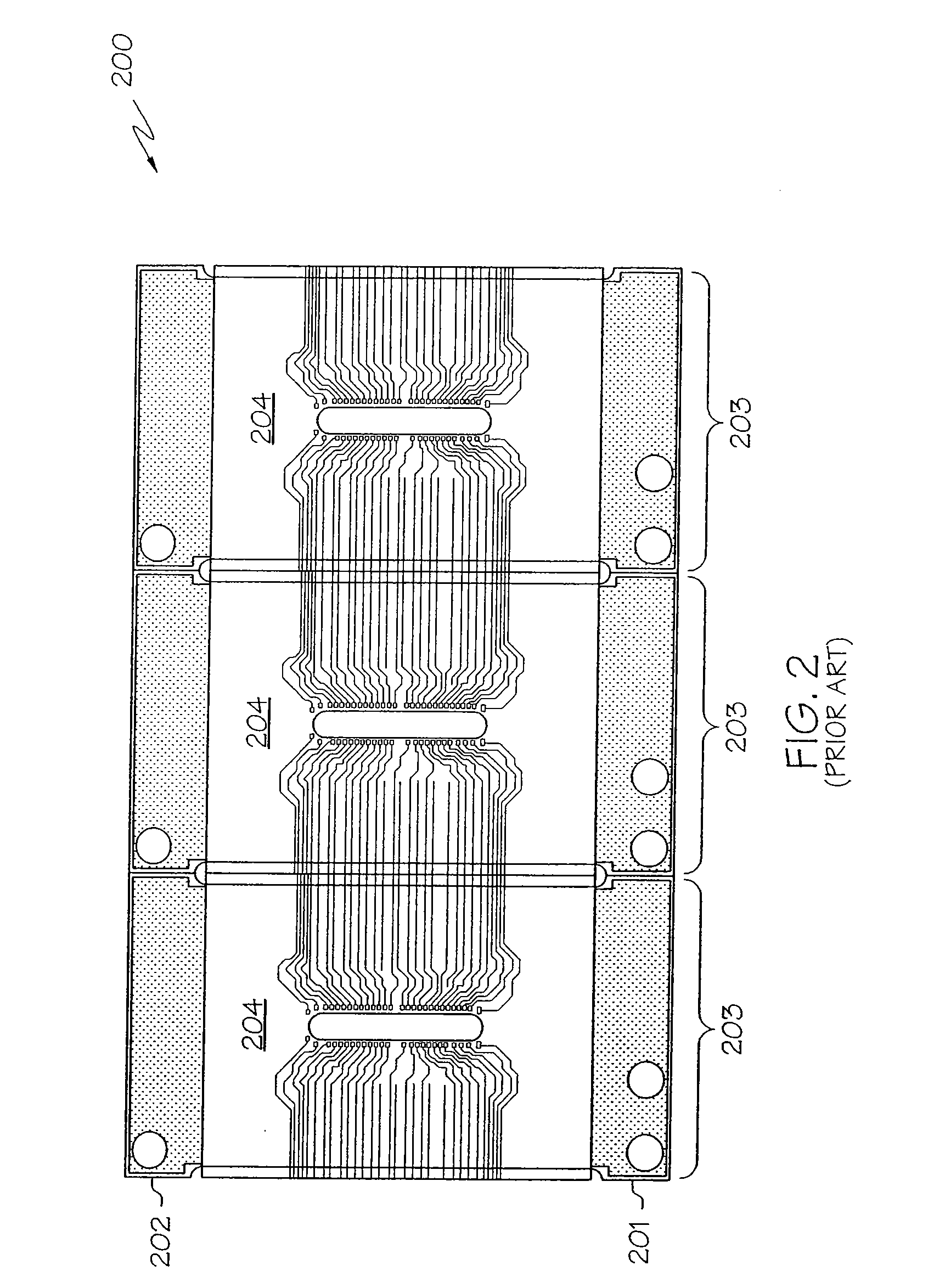

[0027] As stated earlier, FIG. 2 is an example of a standard circuit board 200 used for memory devices such as dual in line memory modules (DIMMs). The circuit board includes a first rail 201, a second rail 202, a number of sites 203 and a patterned area 204. A rail is an area along the edge of a circuit board. The rails 201 and 202 do not generally contain conductive paths, bonding pads or the like. Thus, the rails 201 and 202 do not get etched and conductive material is not removed from the rails 201 and 202. The rails 201 and 202 include a large amount of conductive material such as copper. ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com