MOS field effective pipe and its production

A technology of field effect transistor and channel direction, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve problems such as transistor threshold voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

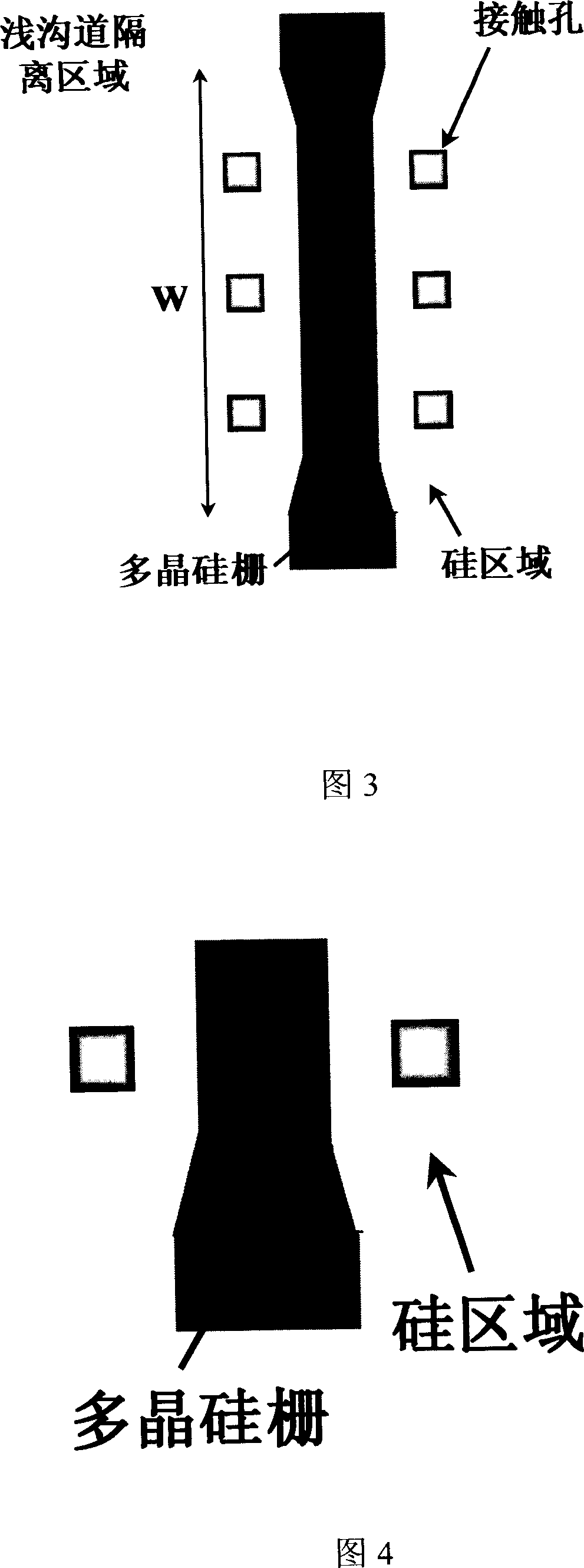

[0013] FIG. 3 is a schematic diagram of a layout of a MOS field effect transistor according to the present invention. A MOS field effect transistor of the present invention has a shallow trench isolation region on both sides of the silicon region, a gate oxide on the top, and a polysilicon gate on the top of the gate oxide. As shown in Figure 3, the width of the polysilicon gate of the MOS field effect transistor, in the W direction, is from somewhere in the silicon region close to the junction of the silicon region and the shallow trench isolation region to the junction of the silicon region and the shallow trench isolation region increases linearly. Fig. 4 is a partial enlarged view of the schematic diagram of the layout of the MOS field effect transistor of the present invention. As shown in Figure 4, the width of the polysilicon gate at the position of length b in the silicon region at the junction of the silicon region and the shallow trench isolation region is wider tha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com