Enhanced wishbone on-chip bus for leading-in bus code

A bus coding and bus technology, applied in the fields of instruments, electrical digital data processing, sustainable buildings, etc., can solve problems such as difficulty in reducing its power consumption, unsupported bus specifications, etc., to reduce the number of bit inversions and reduce power consumption. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

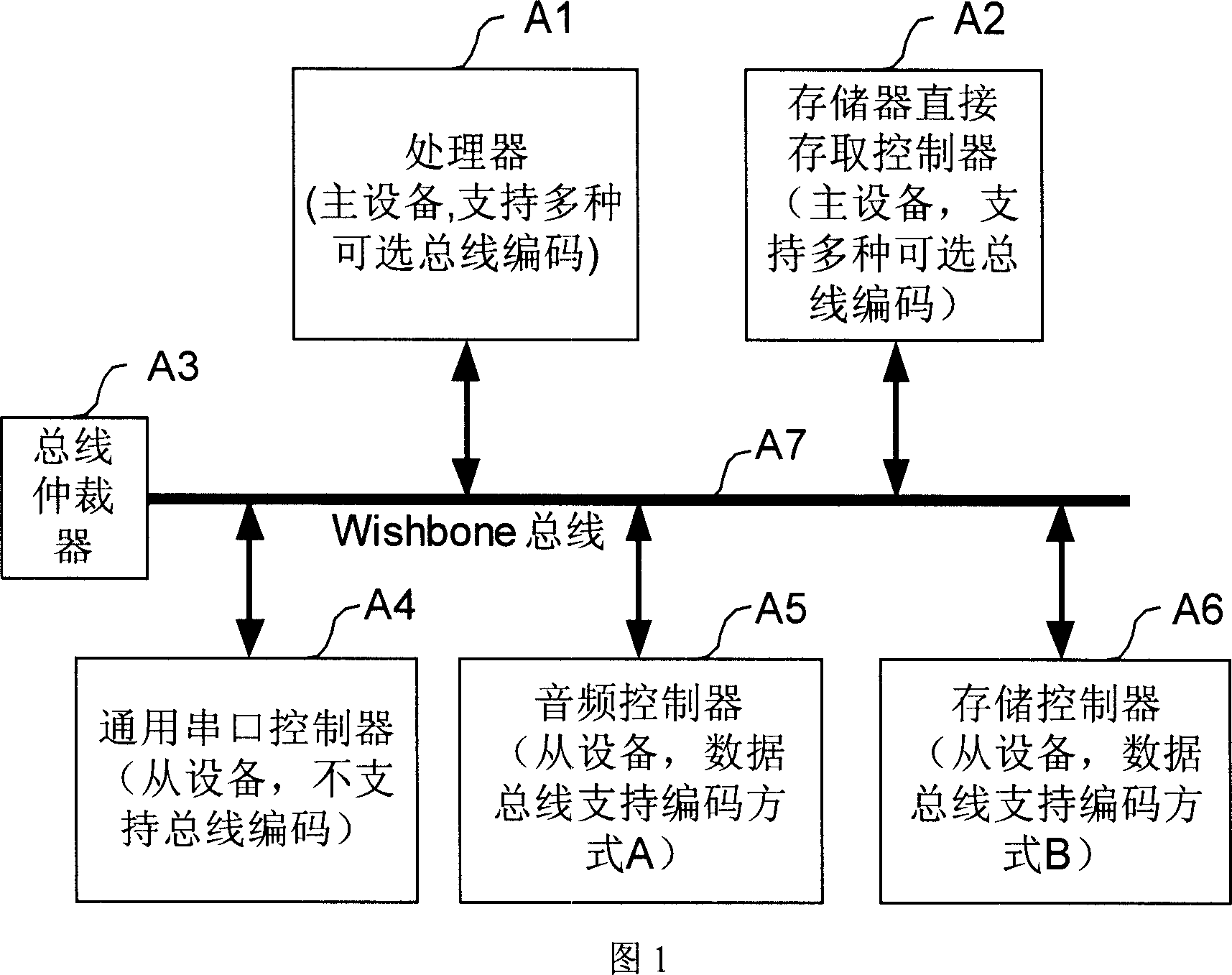

[0024] The architecture diagram of a common system-on-chip interconnected with Wishbone bus is shown in Figure 1. In a system-on-chip, multiple master devices and multiple slave devices communicate through the Wishbone bus to form a complex chip system. In Figure 1, the bus arbiter uses A3 to select which master device can occupy the bus. The master device includes processor A1 and direct memory access controller A2, both of which support multiple bus encoding methods; the slave device includes general serial port controller A4, audio controller A5 and memory controller A6. Universal serial port controller A4 does not support bus encoding, the data bus of audio controller A5 supports bus encoding mode A, the data bus of memory controller A6 supports bus encoding mode B, and the address bus of audio controller A5 and memory controller A6 does not support bus encoding. Generally, since the address changes continuously in most cases and the value of the data bus changes randoml...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com