Programmable asynchronous triggering time delayer, and method of use

A trigger and delay technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

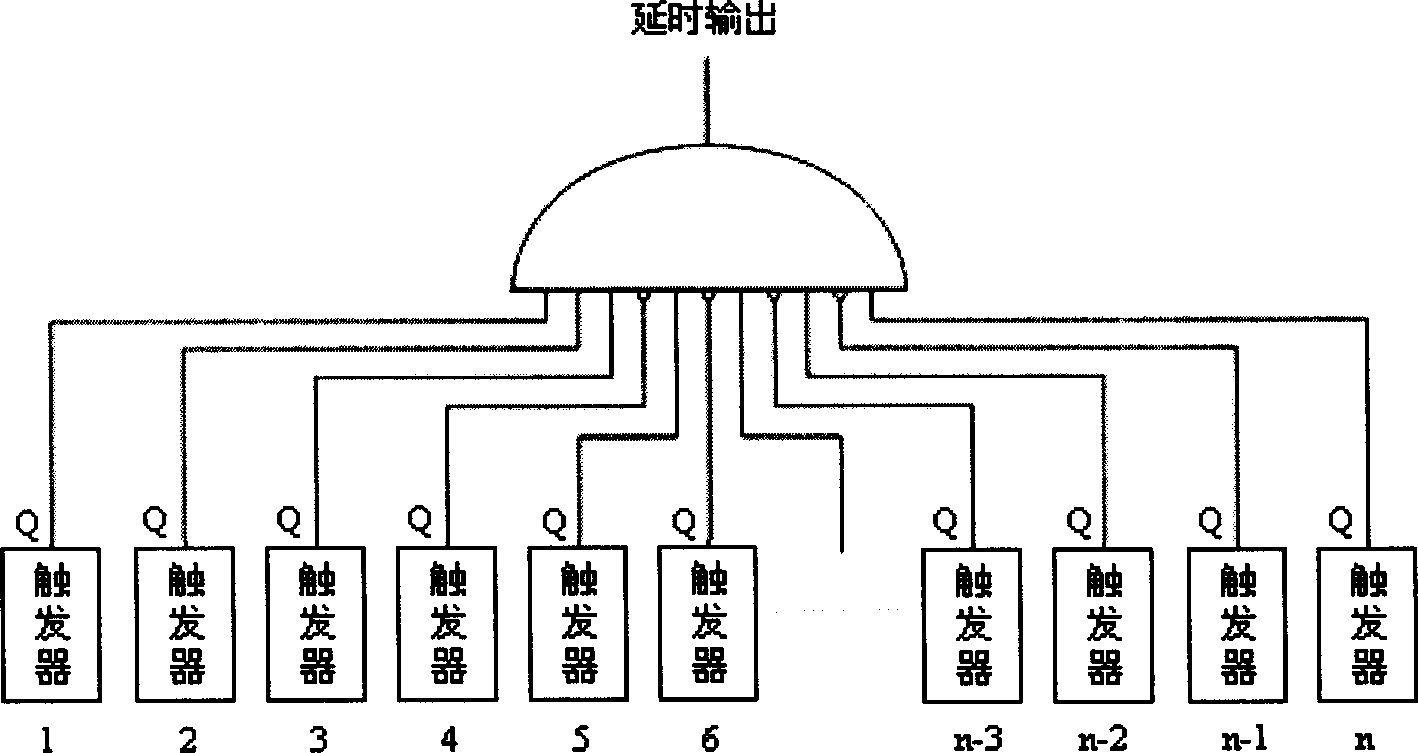

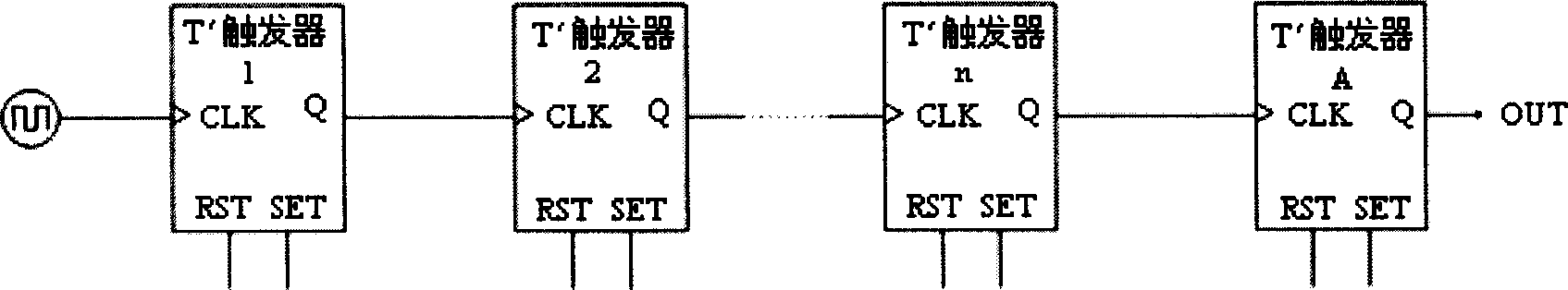

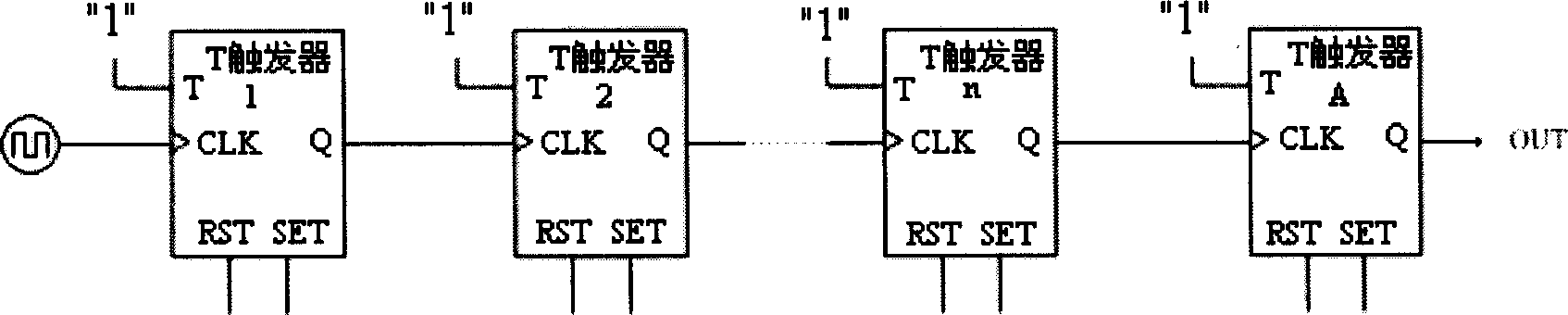

[0016] The circuit structure of the programmable asynchronous trigger delay device of the present invention is as follows: figure 2 As shown, it includes n T' flip-flops, and the n T' flip-flops are connected one by one in turn, the output terminal of the previous T' flip-flop is connected with the CLK terminal of the next T' flip-flop, and the first T' flip-flop The CLK terminal of the ' flip-flop is connected to the external clock pulse, and the SET and RST terminals of these T' flip-flops are the input terminals of the count value, and the first T' flip-flop to the nth T' flip-flop correspond to the input binary From the lowest bit to the highest bit of the data, the present invention also includes the n+1th T' flip-flop, the CLK end of the T' flip-flop is connected to the output end of the nth T' flip-flop, and the output of the T' flip-flop The terminal is the delay signal output terminal, and the number n of the T' flip-flops is greater than or equal to the number of di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com