Stacked layered type semiconductor memory device

A storage device and semiconductor technology, applied in the fields of semiconductor devices, semiconductor/solid-state device components, information storage, etc., can solve the problems of low chip yield and excessive chip economy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

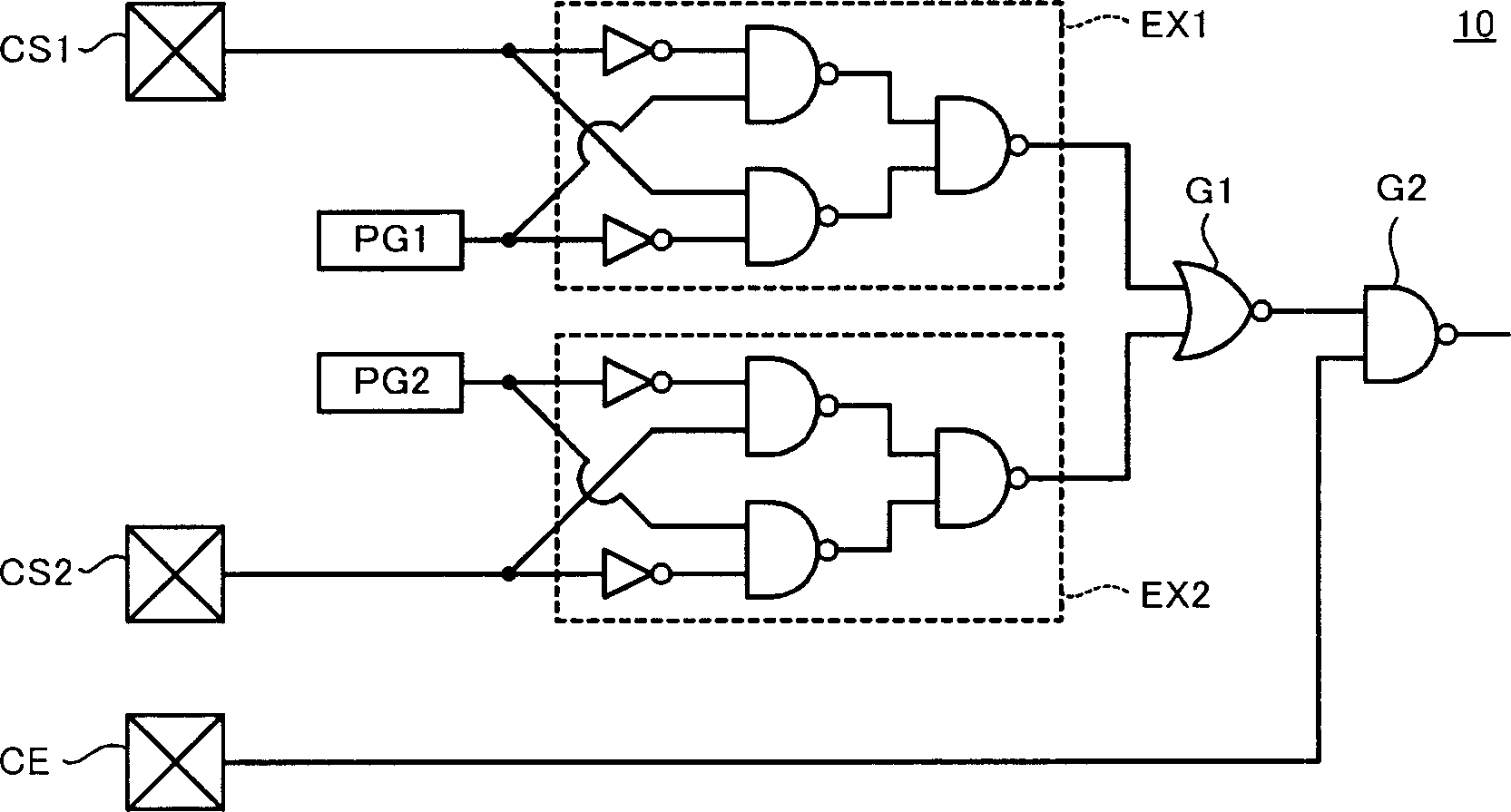

[0021] Hereinafter, embodiments of the present invention will be described with reference to the drawings.

[0022] 1. Lamination of semiconductor memory devices

[0023] figure 1 It is a schematic perspective view of an example of three-dimensional mounting of a stacked semiconductor memory device according to an embodiment of the present invention. In this semiconductor memory device, four identical memory cell array chips C1-C4 are laminated to obtain a memory capacity that is four times the average area. These chips C1 to C4 correspond to the chip layer of the present invention.

[0024] In the chips C1 to C4, a plurality of chip select pads CS1, CS2 and one chip enable pad CE are respectively formed. Also, for simplicity in figure 1 It is not recorded in , but other pads necessary for storage operations, such as address or I / O, control pads, etc., are also formed. The number of chip select pads can be taken arbitrarily according to the number of stacked chips. In th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com