Display device, driving method thereof, and element substrate

A technology for display devices and light-emitting elements, which is applied to electrical components, lighting devices, static indicators, etc., to achieve the effects of suppressing changes in current values, high image quality, and reducing defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

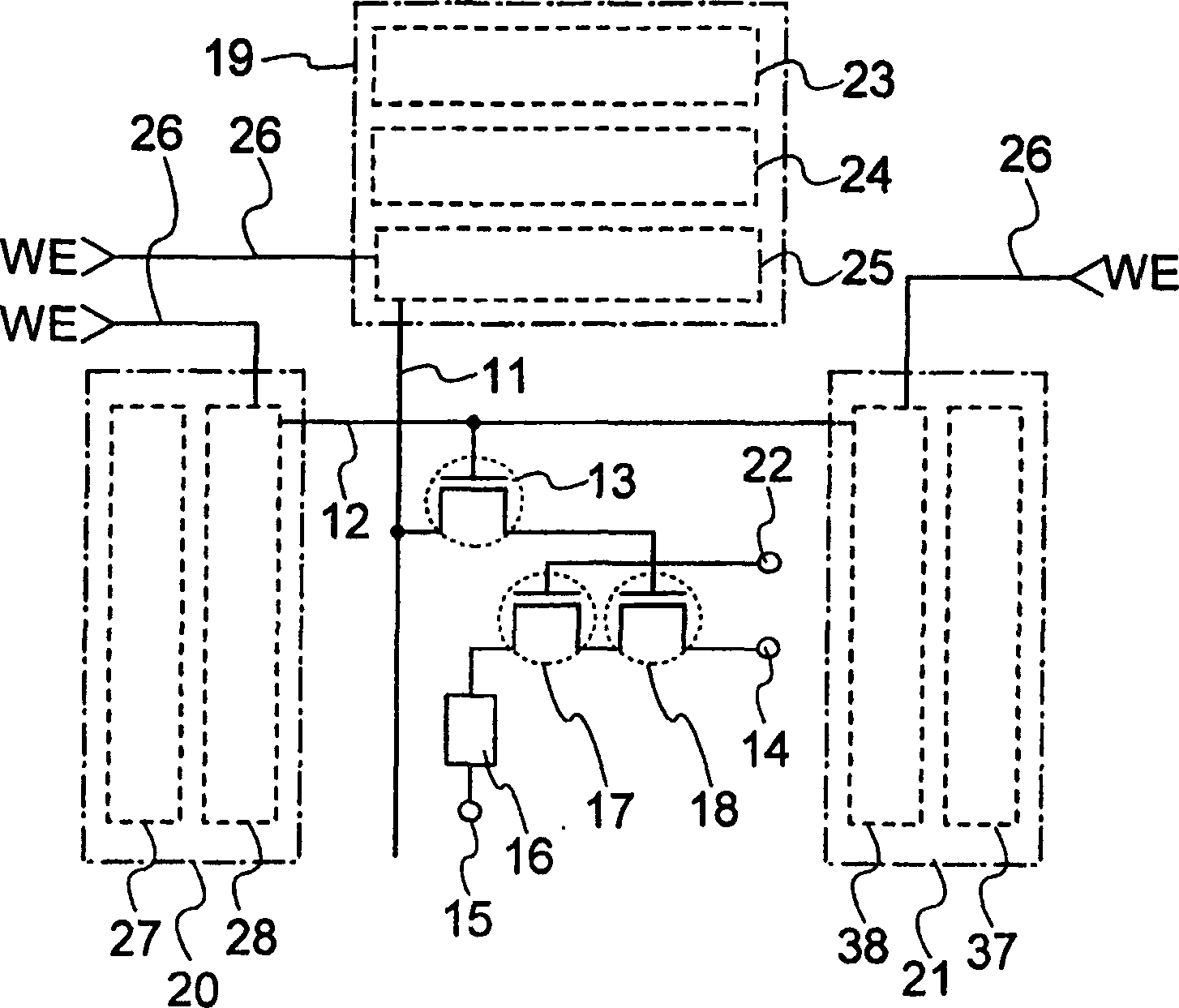

Embodiment 1

[0080] The structure of the light emitting element as a component of the present invention is explained below. The light emitting element has a laminated structure of a conductive layer, an electroluminescent layer, and a conductive layer formed over a substrate having an insulating surface composed of glass, quartz, metal, organic material, or the like. The light-emitting element may be a stacked type including an electroluminescent layer formed of a plurality of layers, a single-layer type including an electroluminescent layer formed of a single layer, or a layered type including an electroluminescent layer formed of a multilayer with unclear boundaries. mixed types. Moreover, the light-emitting element can adopt any one of the following two structures according to the direction of light emission, that is, a forward stacked structure in which a conductive layer corresponding to the anode, an electroluminescent layer, and a conductive layer corresponding to the cathode are st...

Embodiment 2

[0085] The structure of a tri-state buffer as an example of the components of the present invention is explained below. The tri-state buffer includes NAND 81, NOR 82, inverter 83, P-type TFT 84 and N-type TFT 85 ( Figure 6A ). One of the two input nodes of the NAND 81 is connected to the selection signal line 26, and the other node is connected to the shift register. That is, one of the two input nodes of the NAND 81 is input with a WE signal, and the other node is input with a pulse. One of the two input nodes of the NOR 82 is connected to the selection signal line 26 through the inverter 83, and the other node is connected to the shift register. That is, one of the two input nodes of the NOR 82 is input with an inverted WE signal, and the other is input with a pulse. The source electrode of the P-type TFT 84 is connected to a high-potential power supply 86 , while the source electrode of the N-type TFT 85 is connected to a low-potential power supply 87 .

[0086] Accord...

Embodiment 3

[0090] The time gray scale method employed in the display device of the present invention, that is, the driving method (operation) of the display device of the present invention is explained below. The description will be made with reference to a timing chart in which the ordinate represents the scanning line and the abscissa represents the time, and a timing chart of the gate line Gi in the i-th row (1≤i≤n) ( Figure 7A and 7B ). The frame frequency is about 60Hz, and the time period for writing to the screen at one time is called the frame period. According to this time grayscale method, one frame period is divided into a plurality of subframe periods. The number of divisions is usually equal to the number of grayscale bits, and this is shown in this embodiment.

[0091] noticed that in Figure 7A and 7B The timing diagram shown in is just an example, and the subframe period may be further divided in order to reduce pseudo contours and the like.

[0092] First, describ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com