Static electricity protection method of analog signal input pin with common mode electrical level as its lowest electric potential

A common-mode level, lowest potential technology, applied in circuits, electrical components, electro-solid devices, etc., can solve problems that affect the realization of functions and the normal operation of ICs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

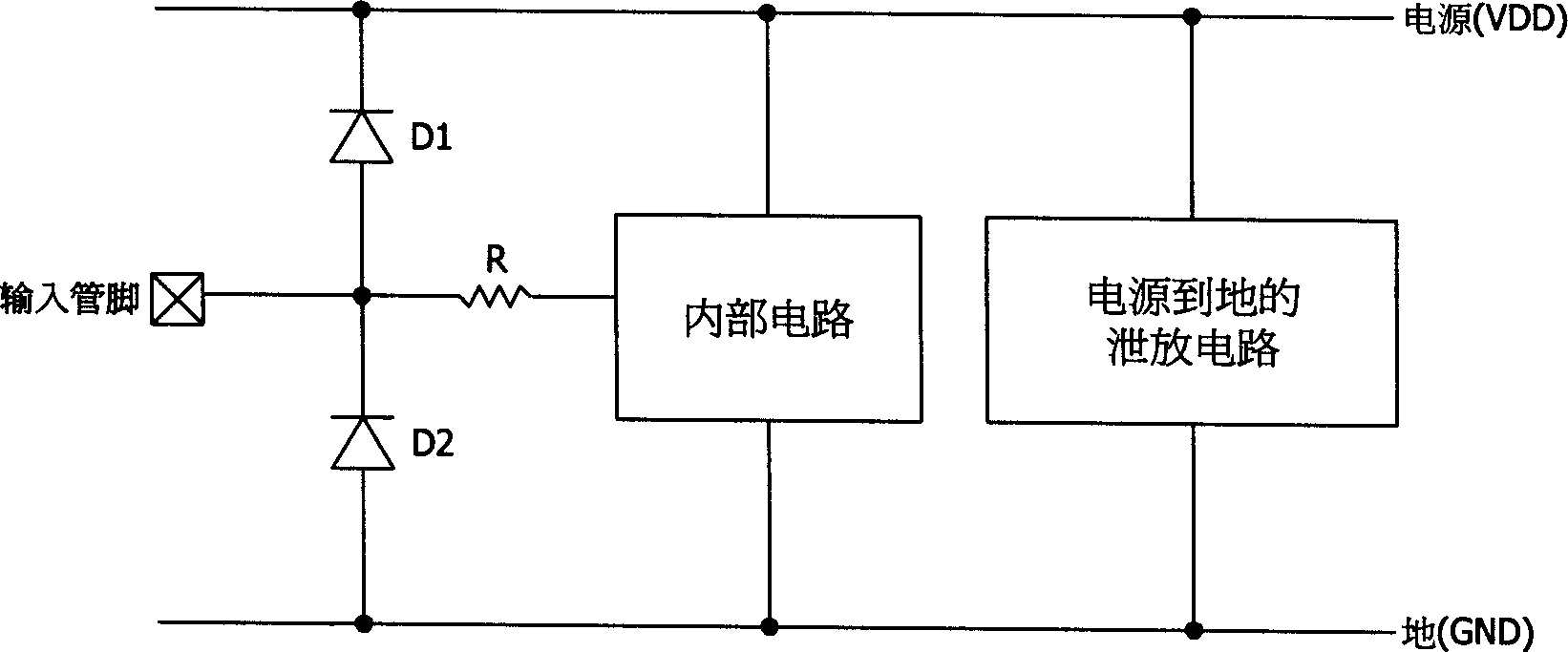

[0013] The present invention proposes an improvement method aiming at that the known protection circuit cannot use the signal input pin lower than the lowest potential in the circuit.

[0014] image 3 Shown is an improved input pin protection circuit of a CMOS integrated circuit, which can realize the electrostatic protection function of the input pin, and does not affect the normal operation of the circuit when the input signal level is lower than 0V. It consists of a PMOS (MP), two resistors R1 and R2, a capacitor C, and a power-to-ground discharge circuit. DP in the figure is the parasitic diode of MP, and D1 is the well in the CMOS integrated circuit (Well) A parasitic diode between the power supply and ground formed with the substrate (Substrate).

[0015] When the integrated circuit using this protection circuit works normally, even if a signal lower than 0V is applied to the input pin, the gate-source voltage (VGS) of MP is still equal to zero and will not conduct, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com