Low-voltage conrol method and device

A technology of working voltage and control circuit, used in static memory, instruments, transistors, etc., can solve problems such as circuit inoperability and DRAM internal circuit false triggering.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

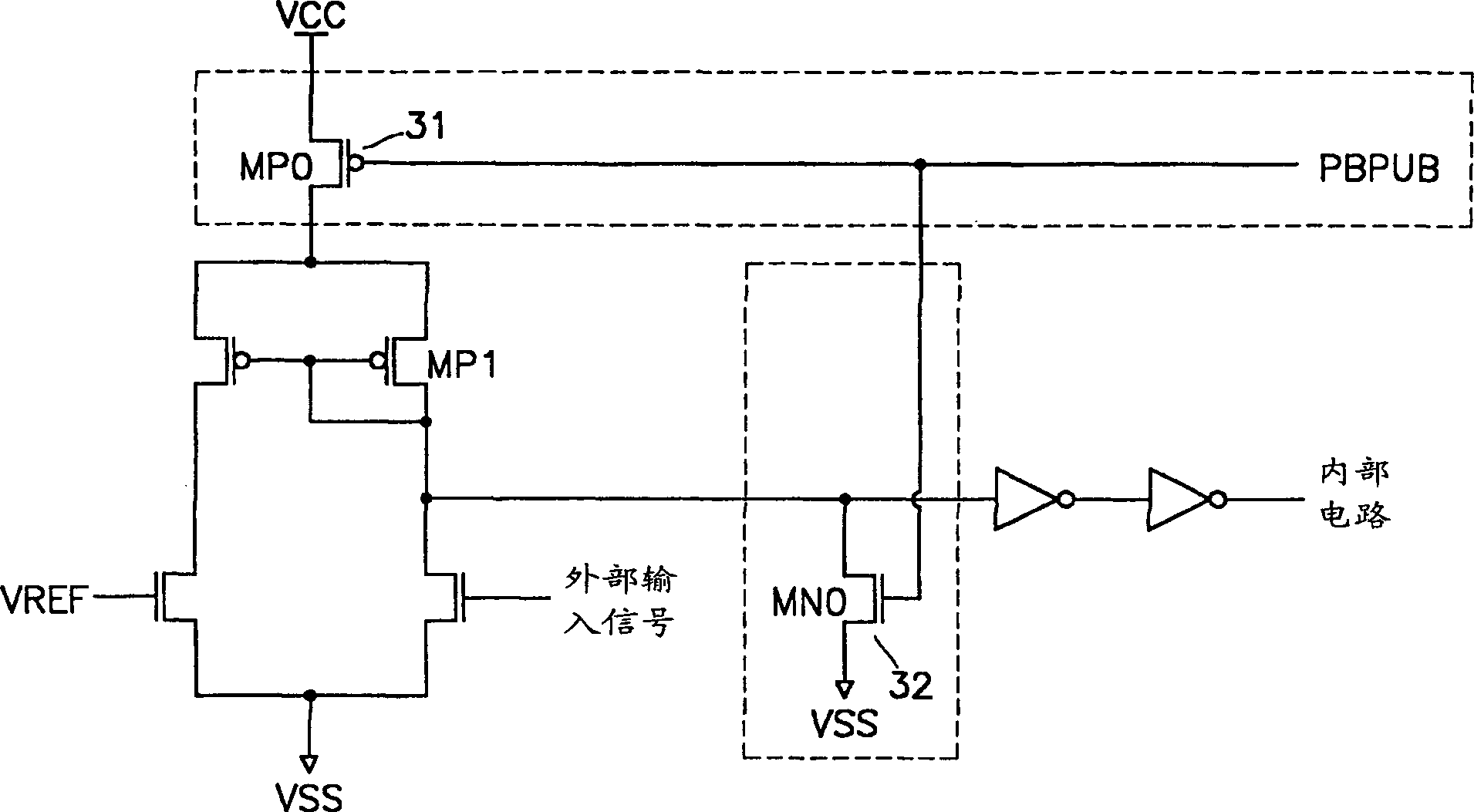

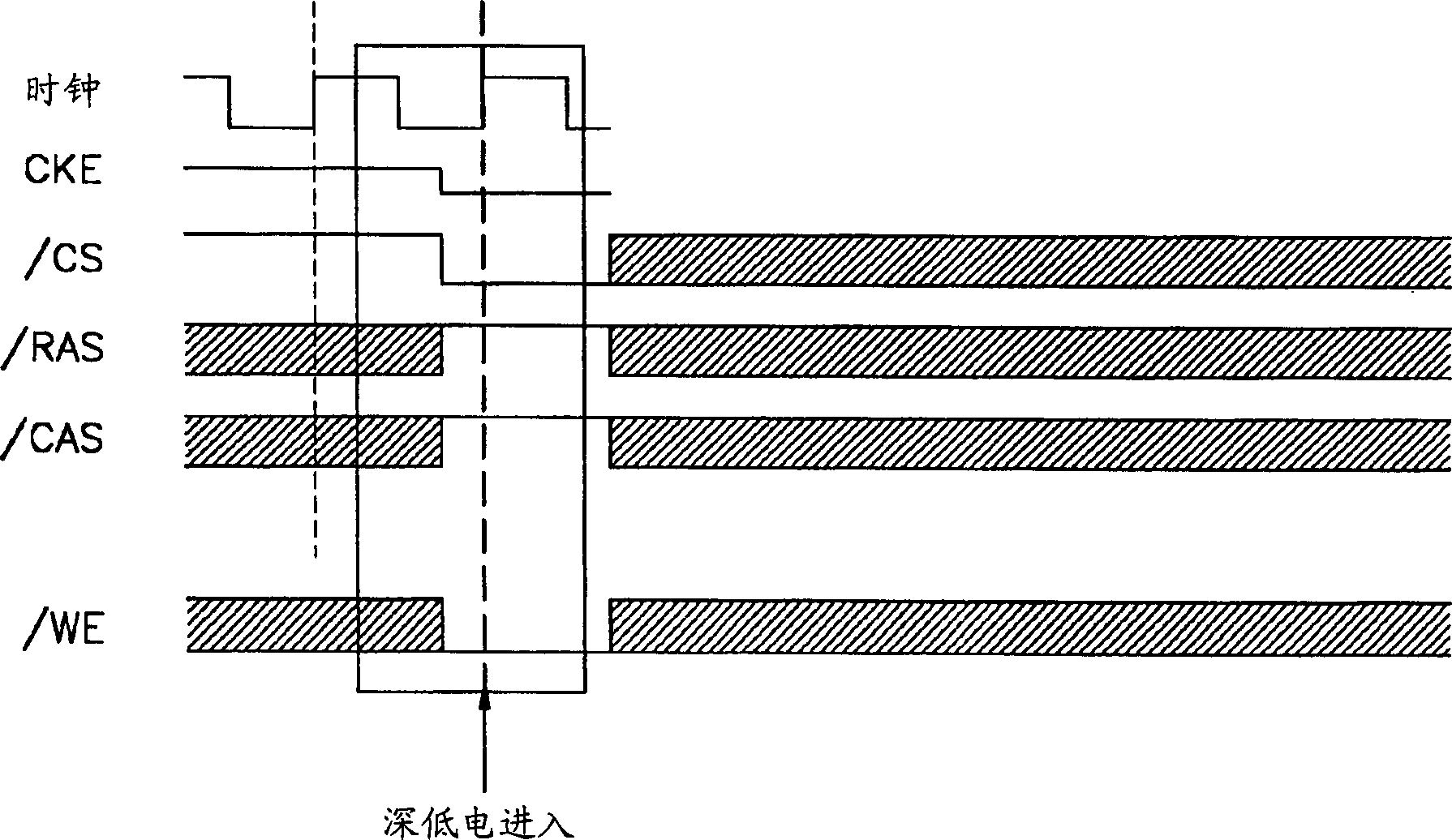

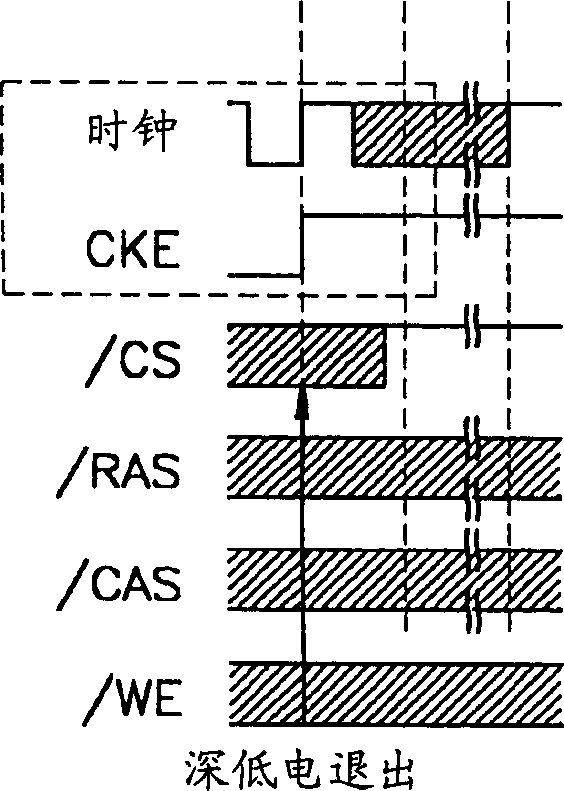

[0042] According to a preferred embodiment of the present invention, there are provided apparatus and methods for operating internal circuits of a DRAM upon entering, exiting, and in a power saving mode of operation. According to several aspects of the present invention, leakage current during power saving mode is reduced or eliminated, the amount of surge during circuit turn-on when exiting power saving mode is reduced, and false triggering of internal circuits is eliminated. Preferred embodiments of the present invention are used to reduce surges when the input buffer and internal power voltage generator are switched on when a semiconductor device enters or exits DPD mode. According to a preferred embodiment of the present invention, for example, by varying the settling time of switching on of the internal power voltage generators, varying the driving capabilities of different internal power voltage generators or buffers, delaying the switching on of different voltage generat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com