Realising method for parallel cascade convolution code hardware decoder

A technology of hardware decoding and implementation methods, which is applied in the field of simplified implementation of error correction code decoding devices, can solve problems such as the limitation of decoder operation speed, and achieve the effects of low decoding time delay, advanced time, and reduced data throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

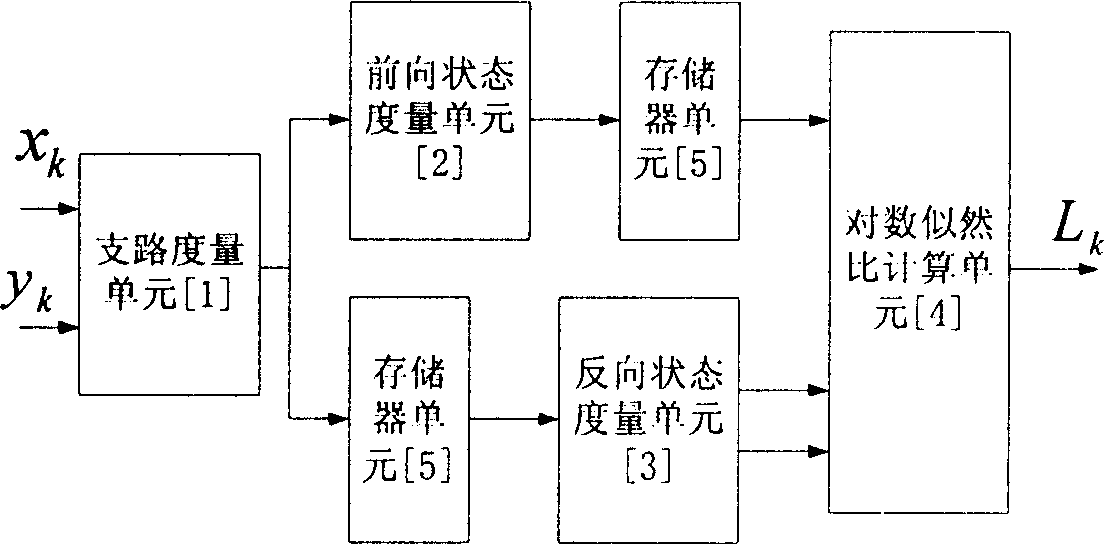

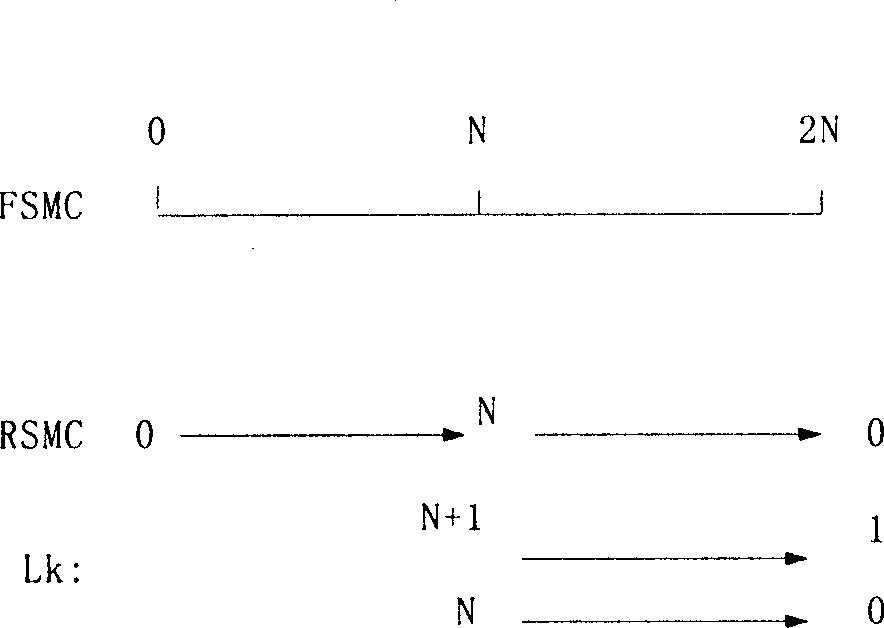

[0022] attached figure 1 .A block diagram of the implementation of the maximum a posteriori probability decoding algorithm in the traditional logarithmic domain. Wherein 1 is the branch measurement unit BMC, 2 is the forward state measurement unit FSMC, 3 is the reverse state measurement unit RSMC, 4 is the logarithmic likelihood ratio calculation unit LLRC, 5 is the memory unit, the size of the memory and the The data length N is the same.

[0023] For the convenience of description, the following agreement is made: the original information bit part x in the data to be decoded k , the check information bit part y in the data to be decoded k , the log likelihood ratio output L k .

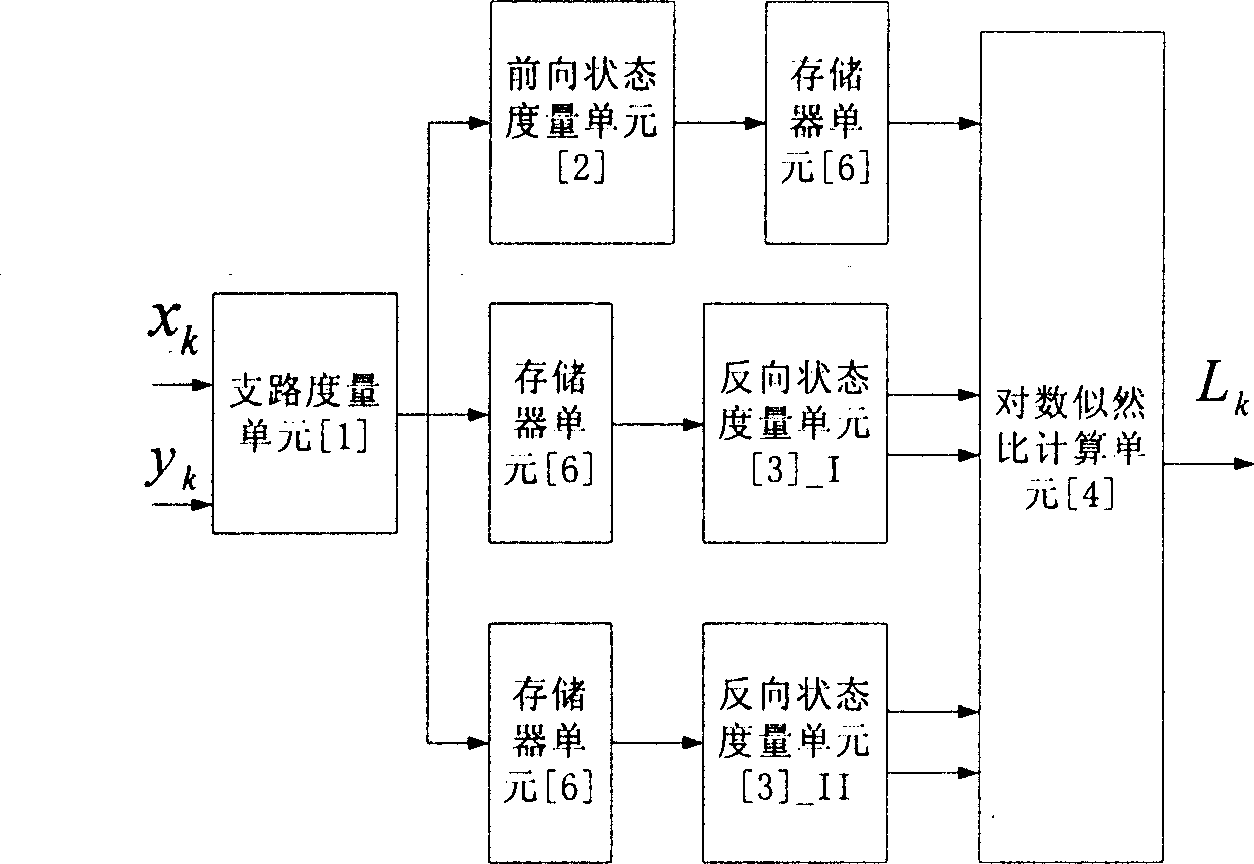

[0024] attached figure 2 . The realization block diagram that the present invention uses. Among them, 3_I and 3_II are two reverse state measurement units RSMC, and 6...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com