Design method of semiconductor chip

A chip design, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, CAD circuit design, etc., can solve the problem of increasing the number of level shifters

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

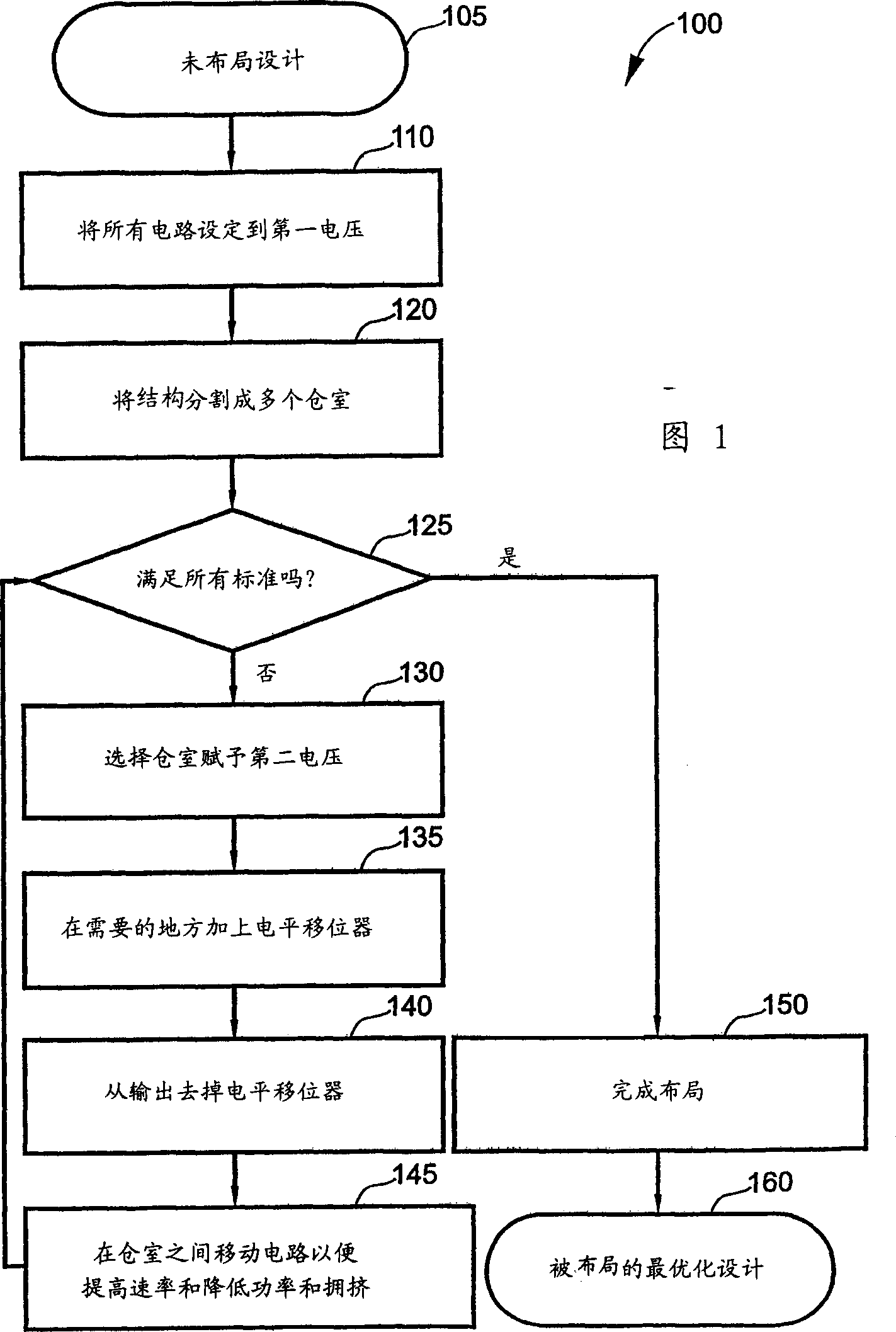

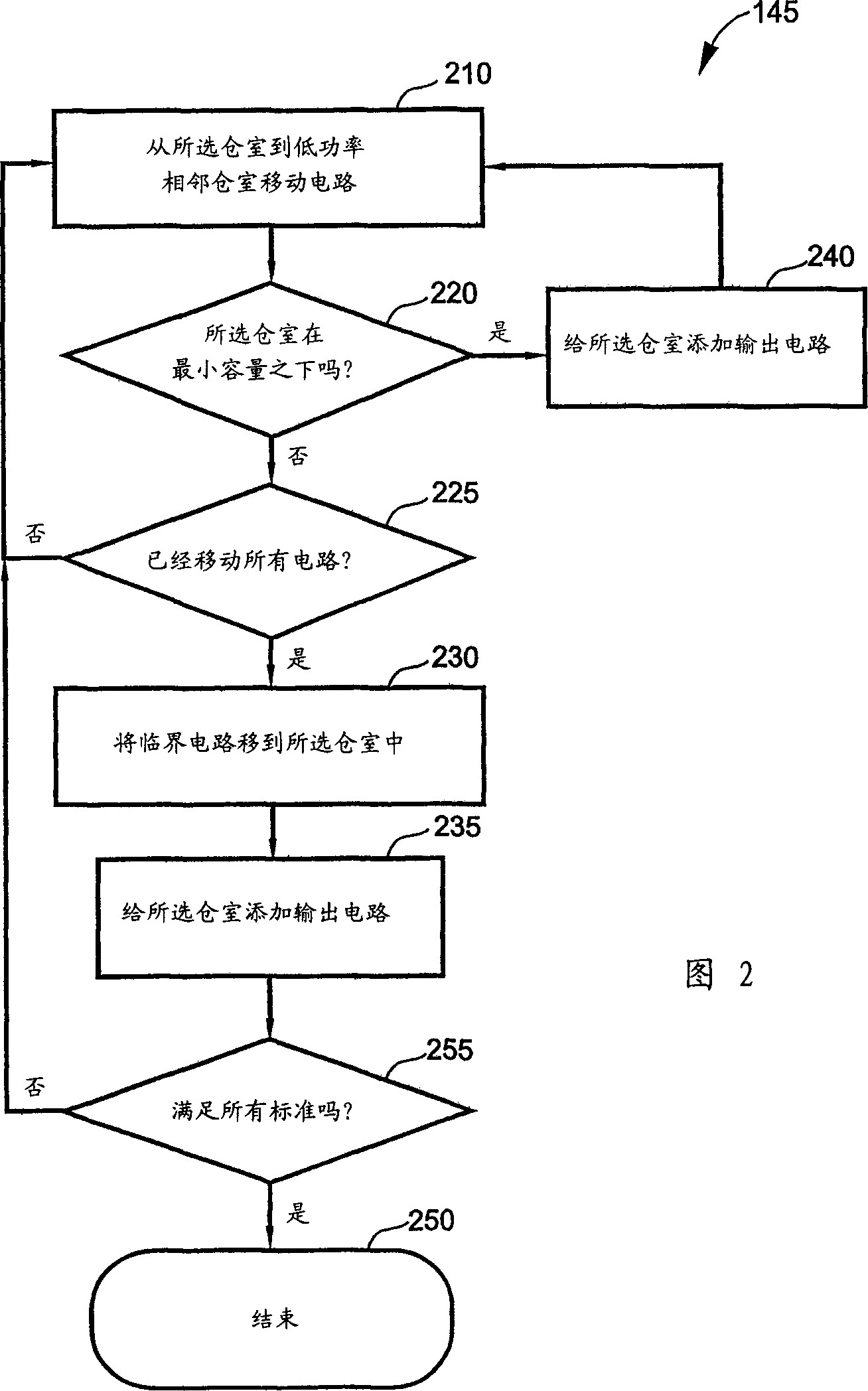

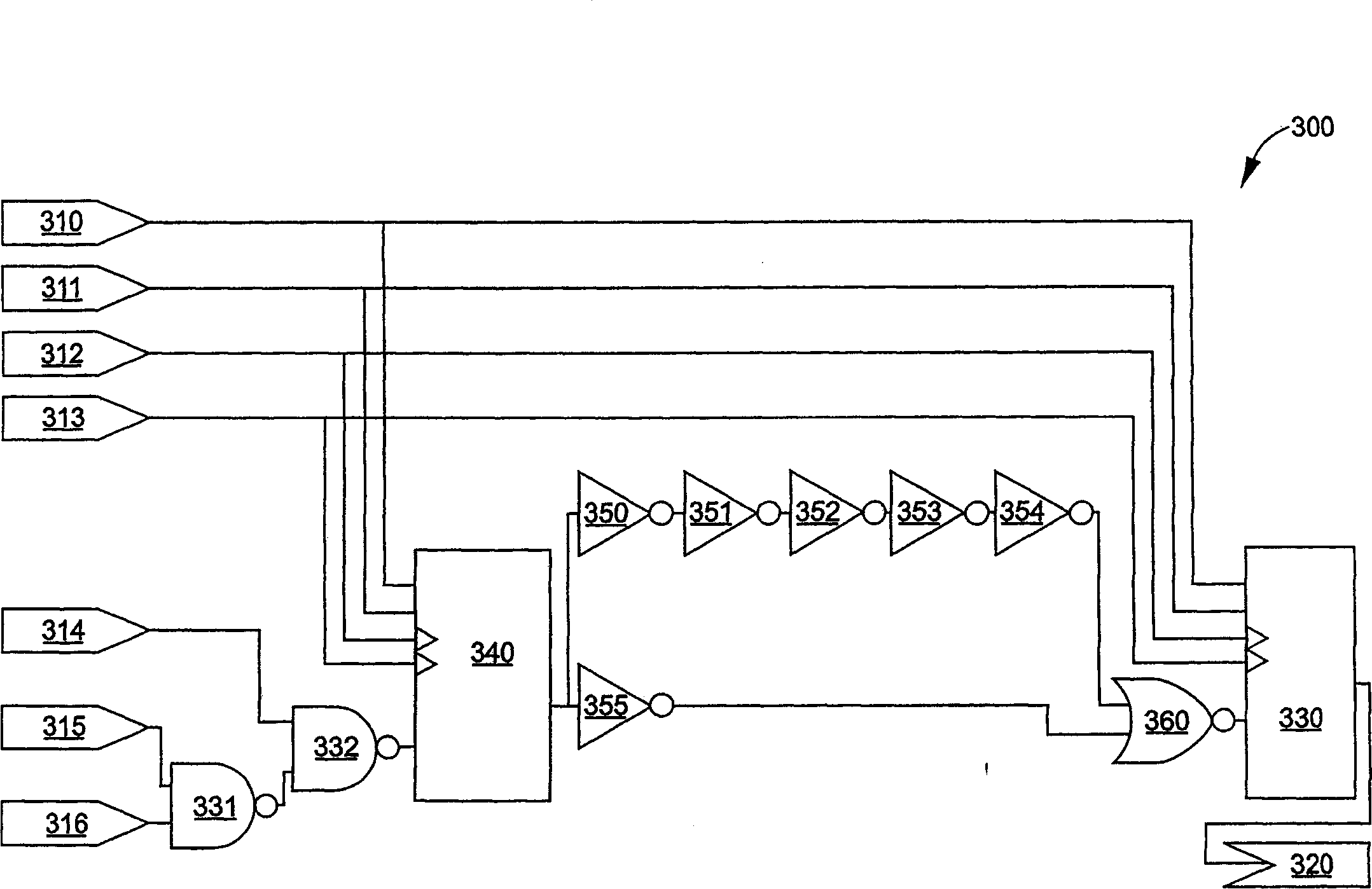

[0019] As noted above, the present invention relates to computer-aided circuit layout on semiconductor chips. For those unfamiliar with the subject, the following overview section briefly introduces some of the concepts related to the layout process. Those skilled in the art of computer-aided circuit layout on semiconductor chips will wish to proceed directly to the details.

[0020] review

[0021] In designing semiconductor chips, computer design tools are used. These tools work and produce a file called a netlist. This netlist contains a description of all gates and the connections between them. Semiconductor chip designers typically work with an analog logic layout of the chip. In other words, the semiconductor chip will perform a certain function, and the designer ensures that the analog chip actually logically performs that function. When the actual chip is ready to be fabricated, the designer uses a layout tool that takes the original netlist and produces the outpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com