Non-volatility internal memory structure

A non-volatile memory technology, applied in electrical components, electric solid-state devices, circuits, etc., can solve serious problems such as increased power consumption of non-volatile memory components, affecting the accuracy of data reading, etc., to reduce power consumption volume effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

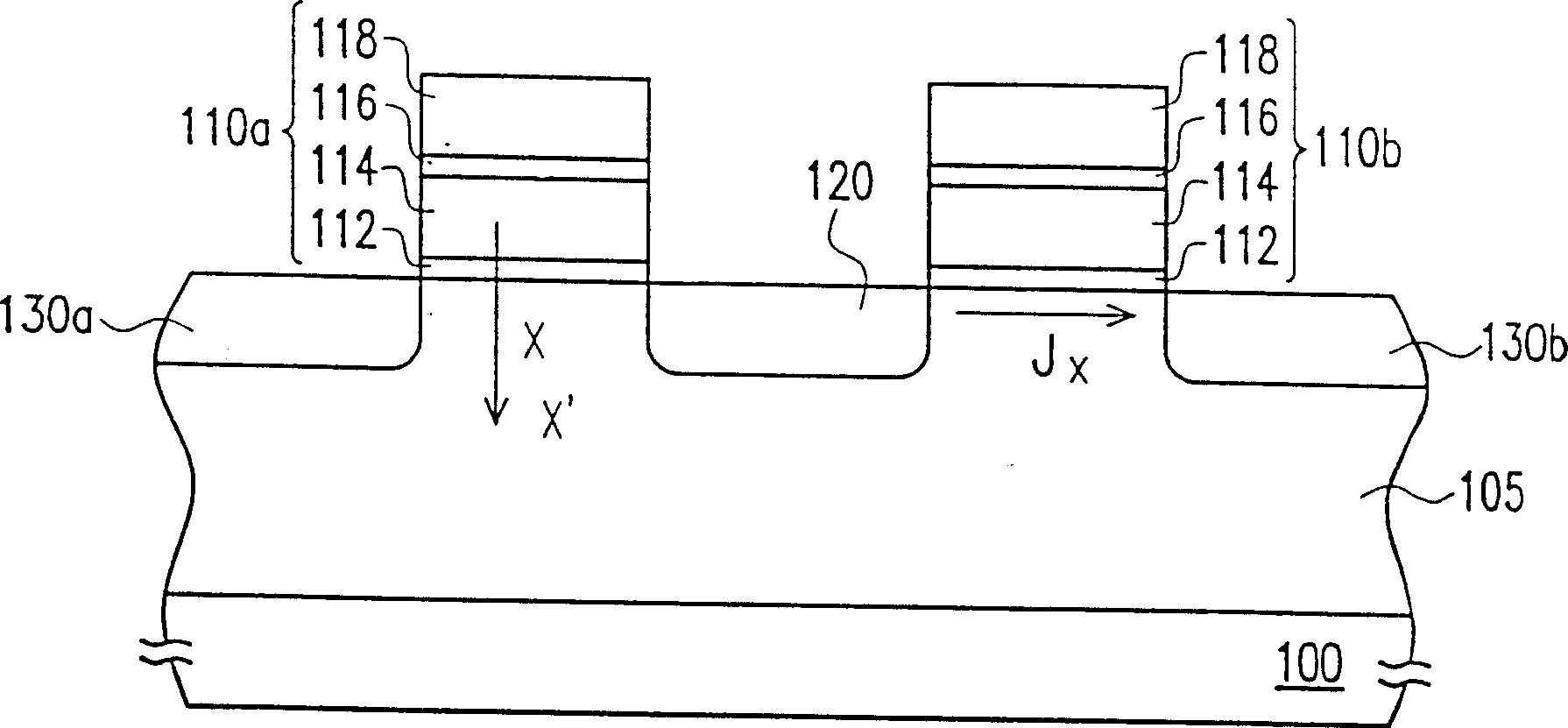

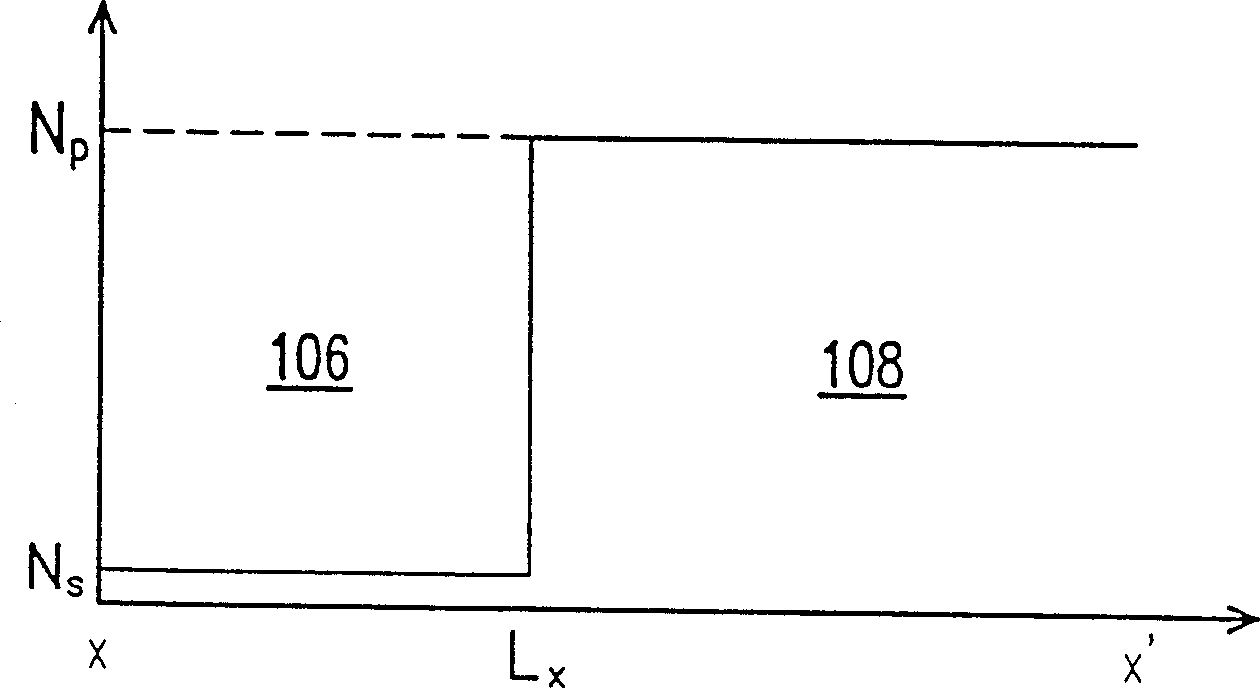

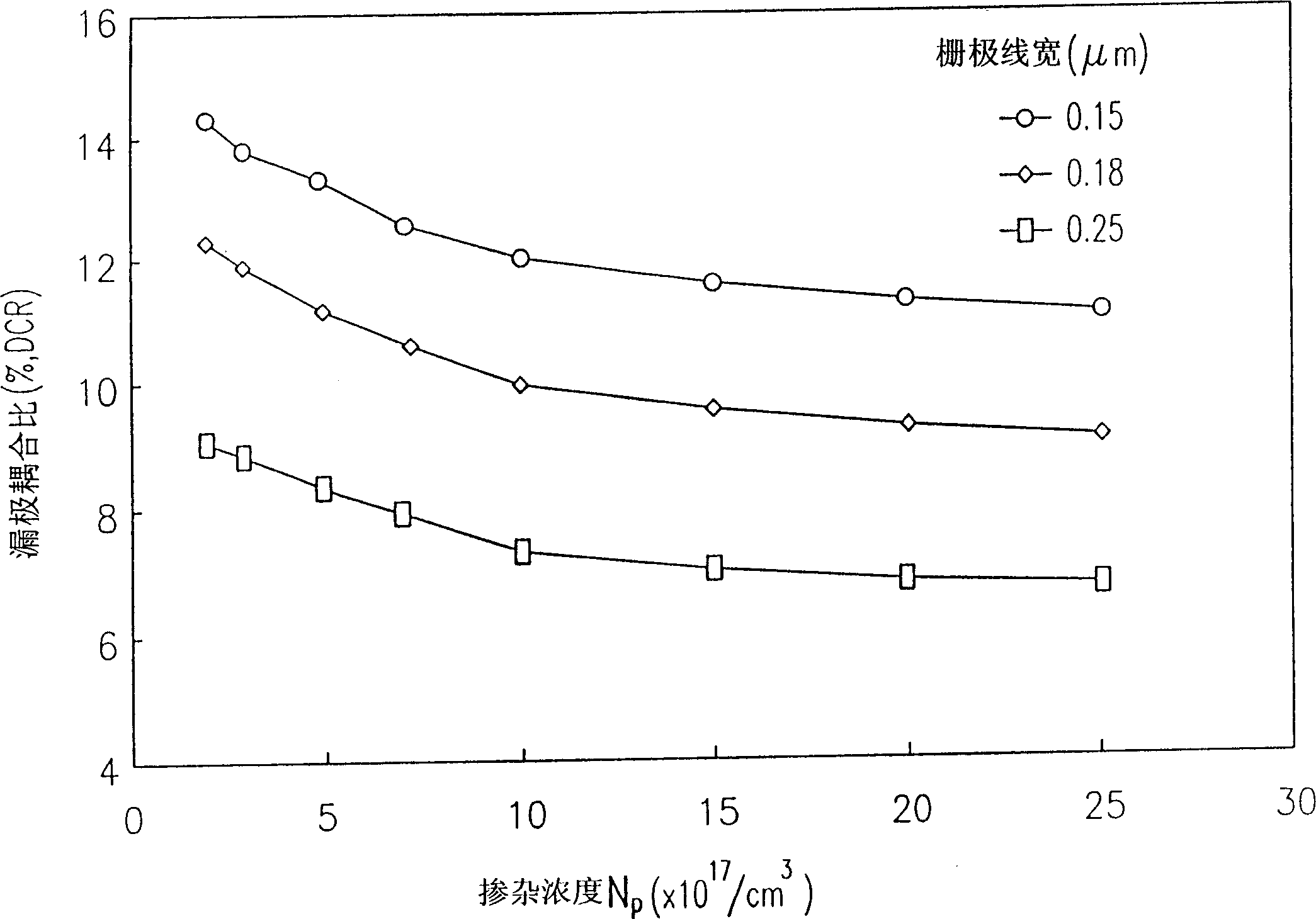

[0020] Please refer to figure 1 , Figure 1A , is the structure of the dual memory unit (Dual-cell) non-volatile memory of the embodiment of the present invention, wherein Figure 1A Shows the vertically stepped channel doping profile (VLCP) in the substrate. like figure 1 As shown, this structure includes a substrate 100, a well region 105 located in the substrate 100, two stacked gate structures 110a and 110b located on the substrate 100, and a common drain region 120 located in the substrate 100 between the two stacked gate structures 110a and 110b , and two source regions 130a and 130b in the substrate 100 outside the two stacked gate structures 110a and 110b. Wherein, the stack gate structure 110a / b includes a tunnel layer (Tunnel Layer) 112, a floating gate (Floating Gate) 114, a dielectric layer 116 and a control gate (Control Gate) 118 stacked from bottom to top. , and the depth of the common drain region 120 and the source region 130a / b is, for example, between 40...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com