Method and apparatus for accelerating processor to read and write scratch memory

A technology for accelerating processors and temporary registers. It is used in program control devices, electrical digital data processing, instruments, etc., and can solve problems such as poor read and write speed, poor performance of read and write registers, and large program capacity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

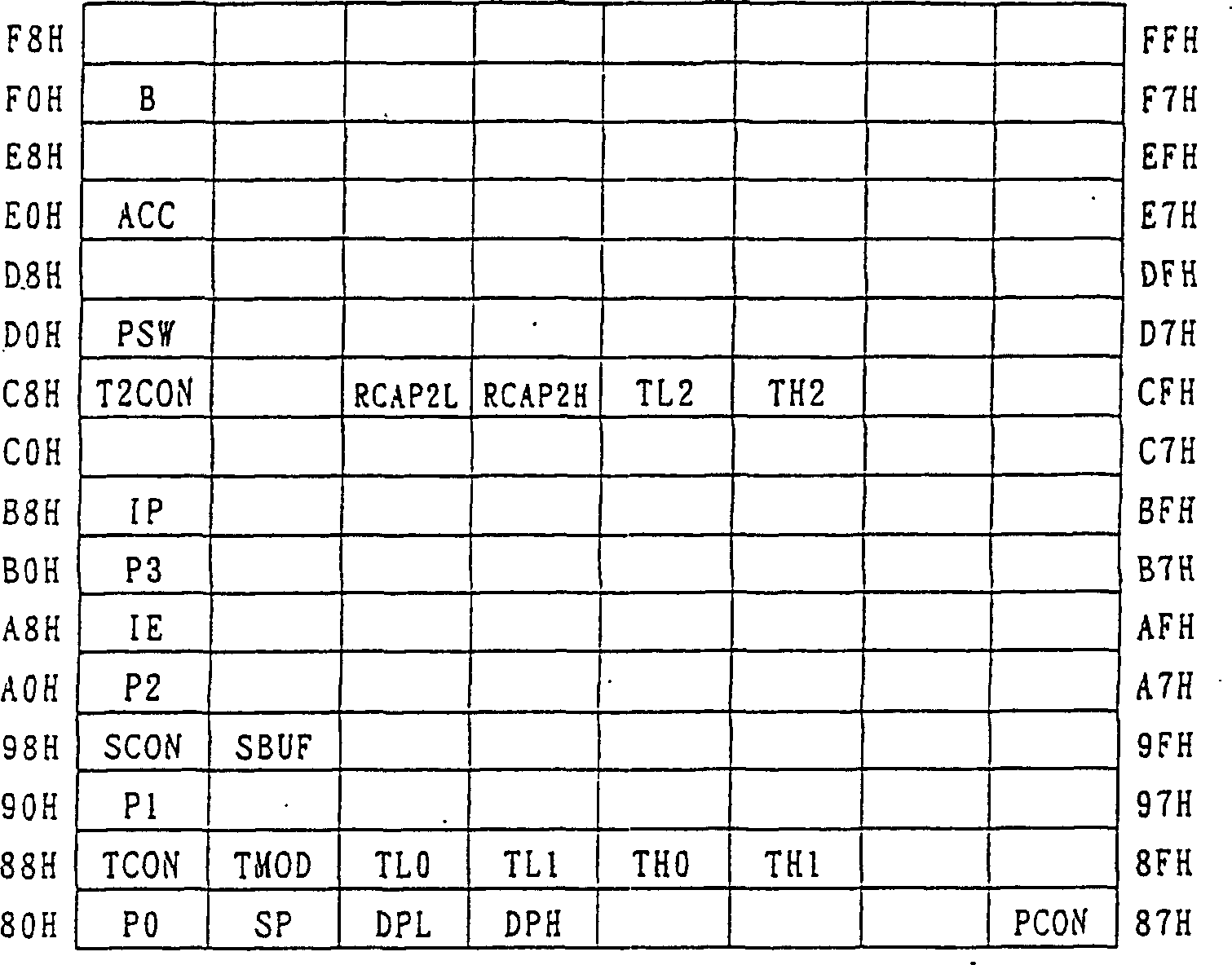

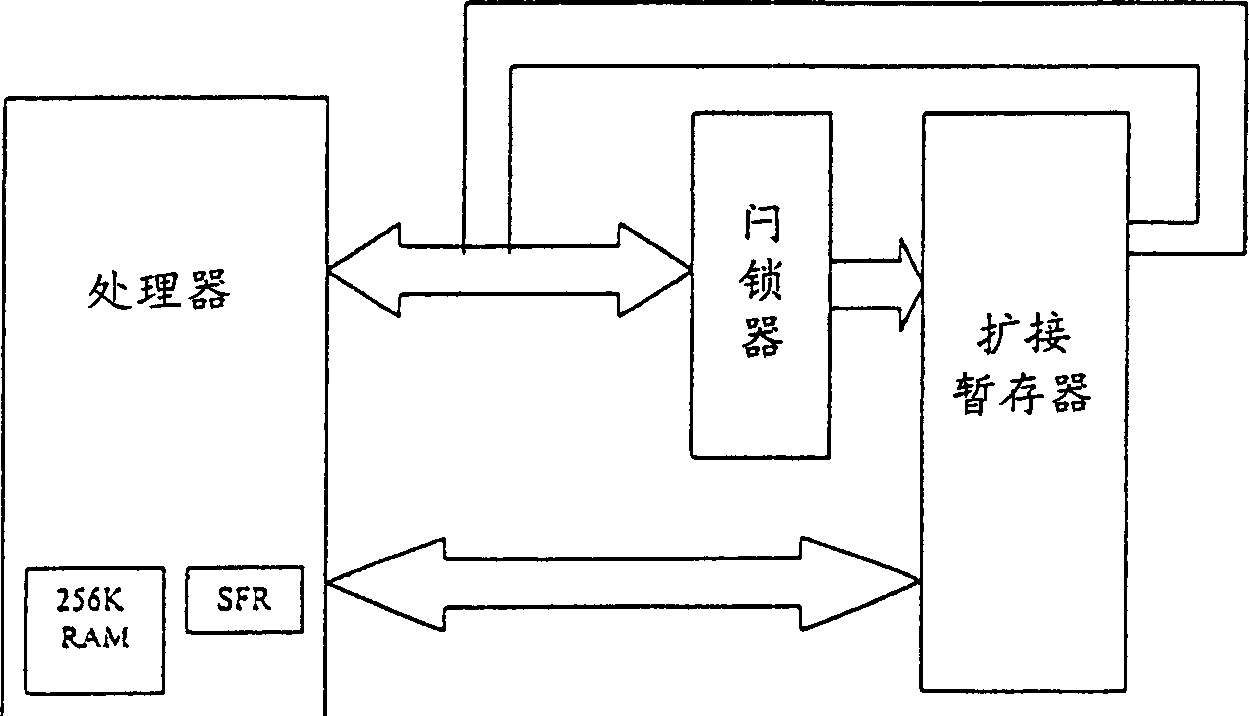

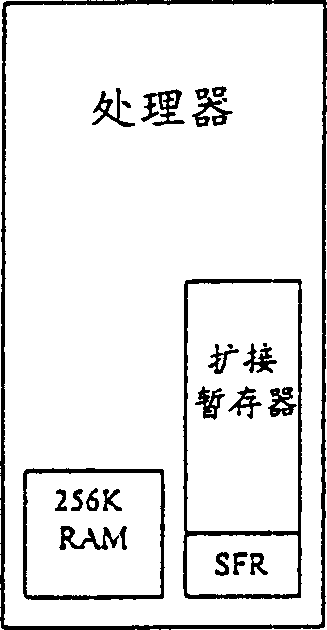

[0021] Firstly, in the present invention, the processor is externally connected with an expansion memory to establish an expansion temporary register. In this embodiment, an 8051 processor is used as an example. The extended register address is mapped to the idle address of the special function register (SFR) in the processor by means of memory mapping (MEMORY MAPPING).

[0022] The SFR is a 128-byte (Bytes) (80H~FFH) directly addressable memory area (see figure 1 As shown), in addition to the existing multiple groups of temporary registers, there are still many idle addresses, so the present invention maps the address of the extended temporary register to the idle address of SFR, so that in the normal operation mode, the The extended scratchpad is simulated as an internal scratchpad, and the extended scratchpad can be read and written by internal data transfer instructions. Compared with the way of reading and writing external scratchpads by external data transfer instruction...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com