Trench MOSFET device with double-diffuser distribution and making method

A trench and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of device breakdown voltage reduction, achieve low on-resistance, prevent breakdown, and avoid reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

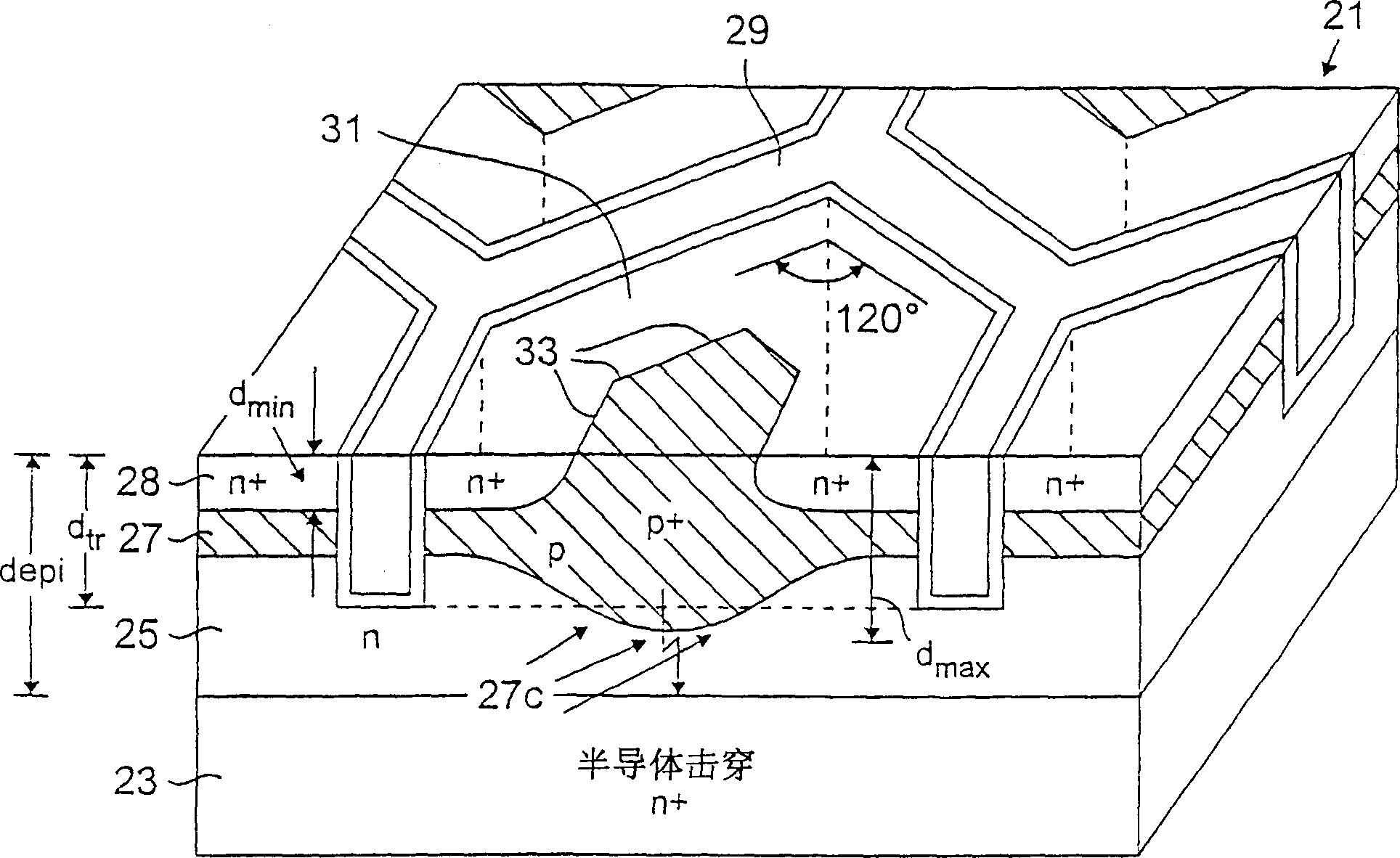

[0051] The invention is explained in more detail below with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. The invention can, however, be embodied in different ways and should not be limited to the embodiments described herein. For example, the description here refers more to N-channel 20 to 30V devices, but clearly other devices are possible.

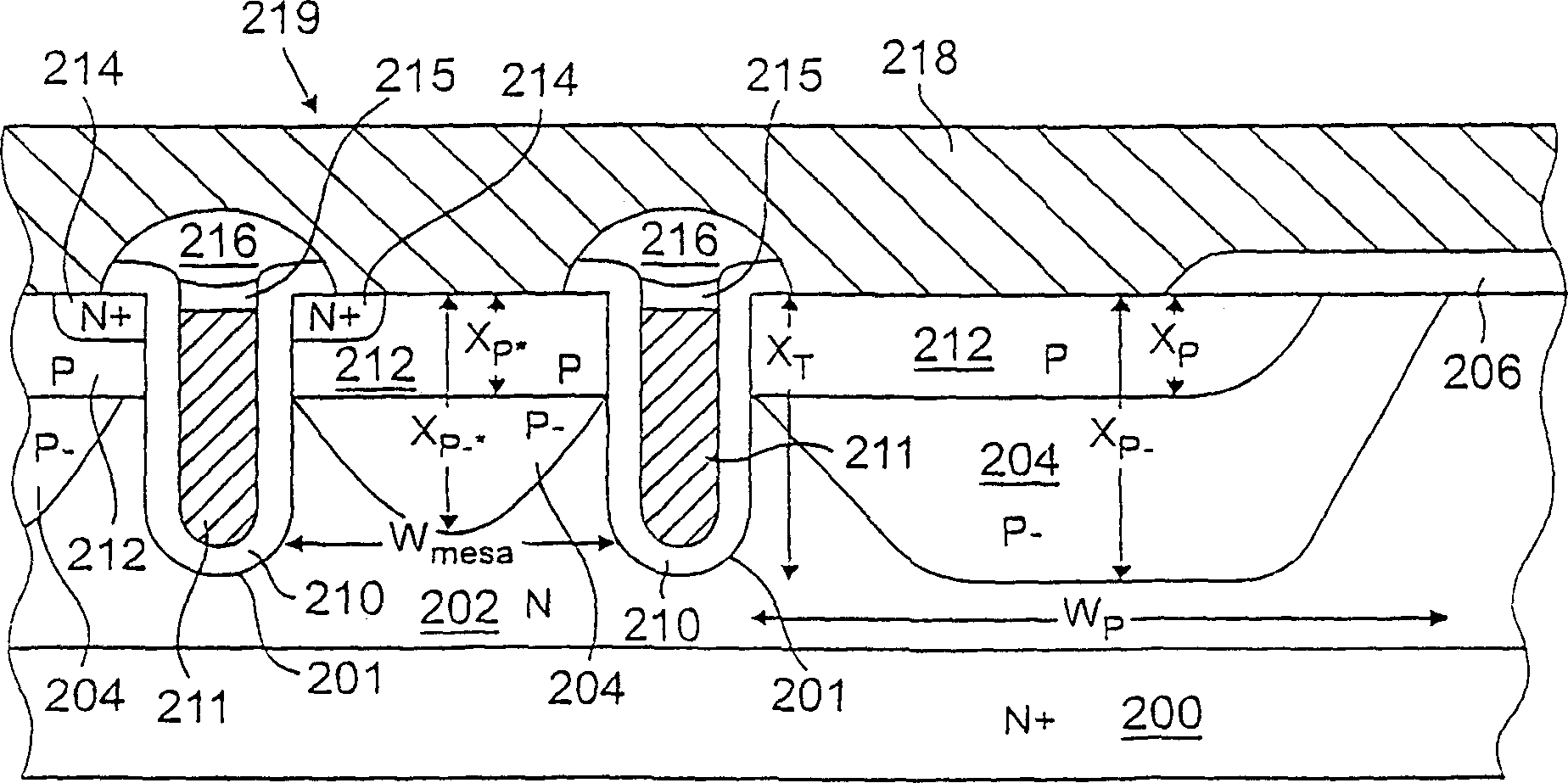

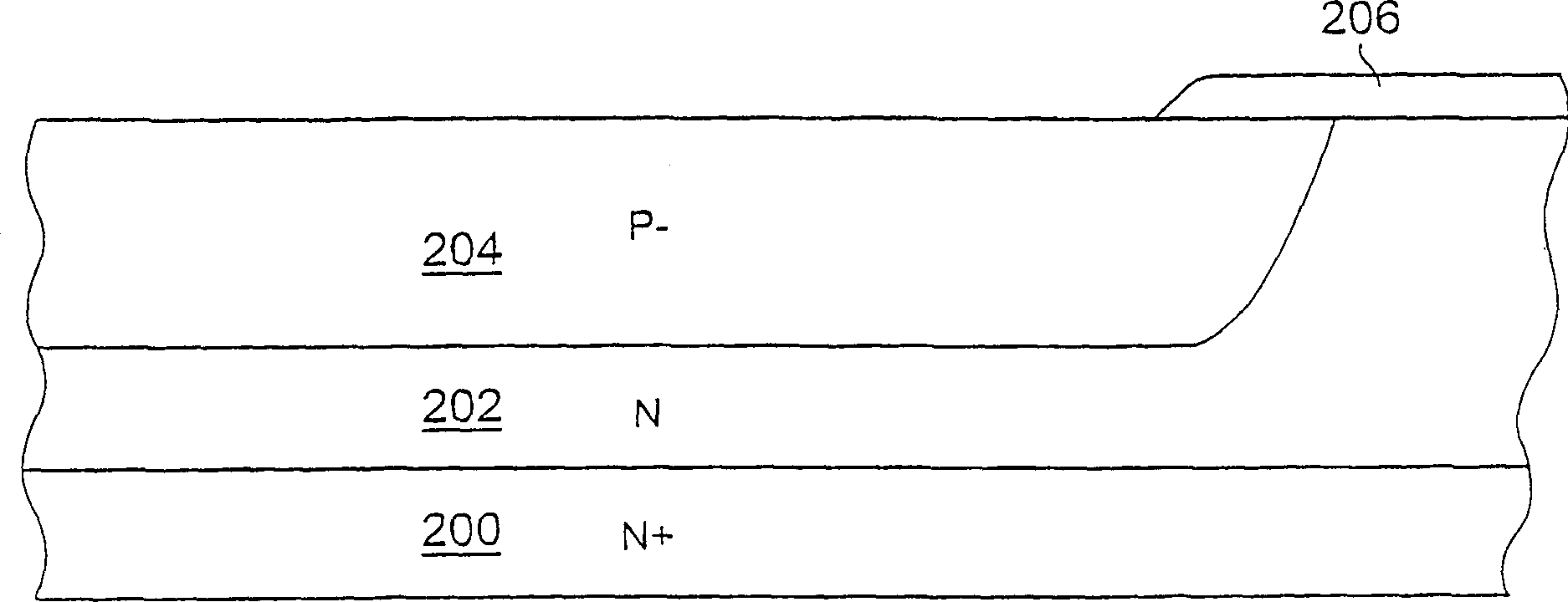

[0052] refer to figure 2 , shows trench MOSFET 219 with N-type epitaxial layer 202 formed on N+ substrate 200 . The N+ substrate 200 is a typical silicon substrate with a thickness ranging from 20 to 25 mils and a resistivity ranging from 0.005 to 0.01 Ω·cm. The N-type epitaxial layer 202 is also typical silicon, with a thickness ranging from 5 to 6 microns and a resistivity ranging from 0.18 to 0.25Ω·cm.

[0053] A trench 201 formed in the epitaxial layer is aligned with the gate oxide 210 and fills a polysilicon (ie, polysilicon) gate electrode 211 . The gate oxide 210 is typica...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com