Low-power-consumption successive approximation analog-to-digital converter based on Split capacitor DAC

A successive approximation type, analog-to-digital converter technology, applied in analog-to-digital conversion, code conversion, instruments, etc., can solve the problems of reducing the accuracy of SARADC comparison results, reducing the accuracy of SARADC, and large kickback noise of dynamic comparators. Achieve low clock feedthrough, small equivalent output capacitance and total capacitance, and reduce kickback noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some implementations of the present invention, not all of the embodiments. The embodiments of the present invention, and all other embodiments obtained by those of ordinary skill in the art without creative work, fall within the protection scope of the present invention.

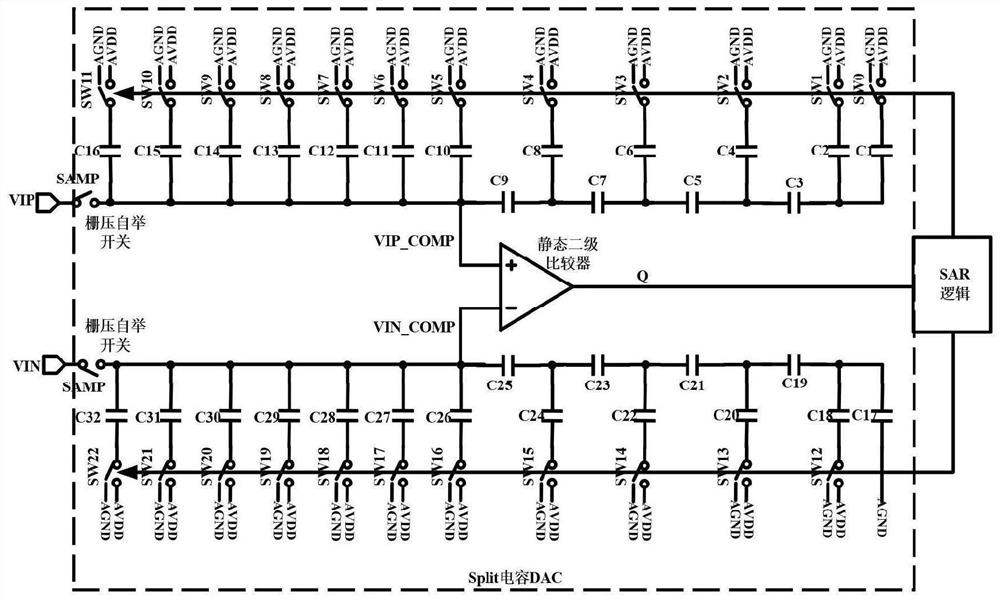

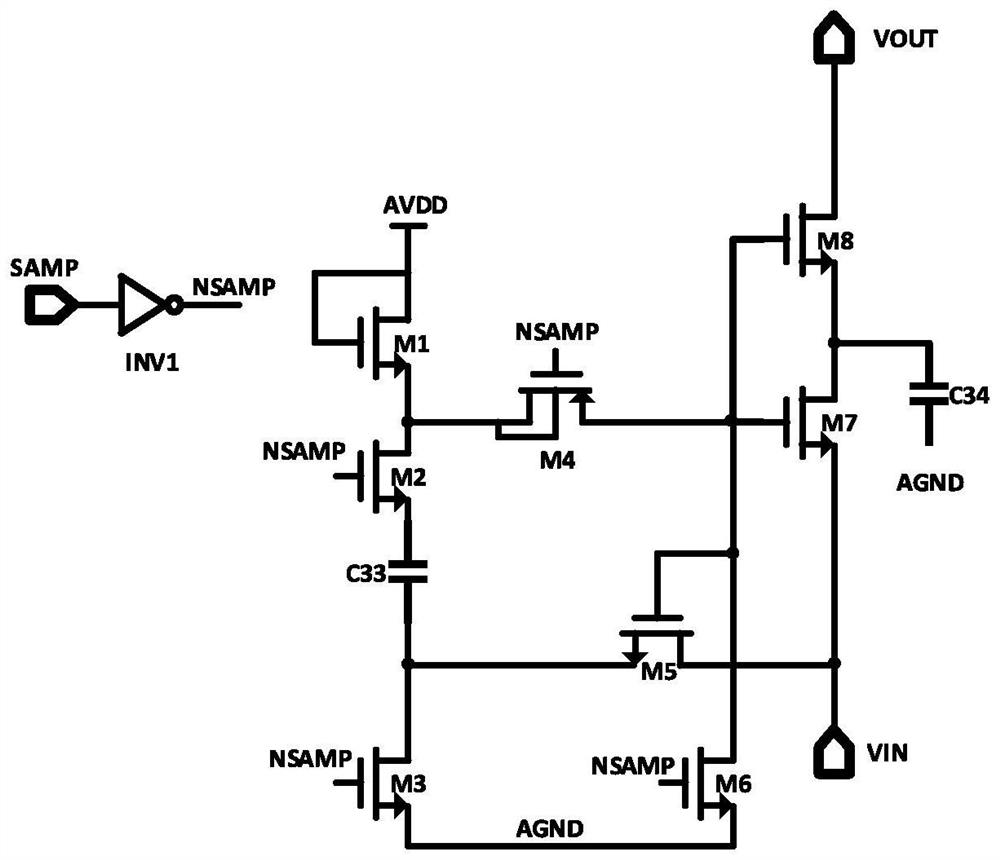

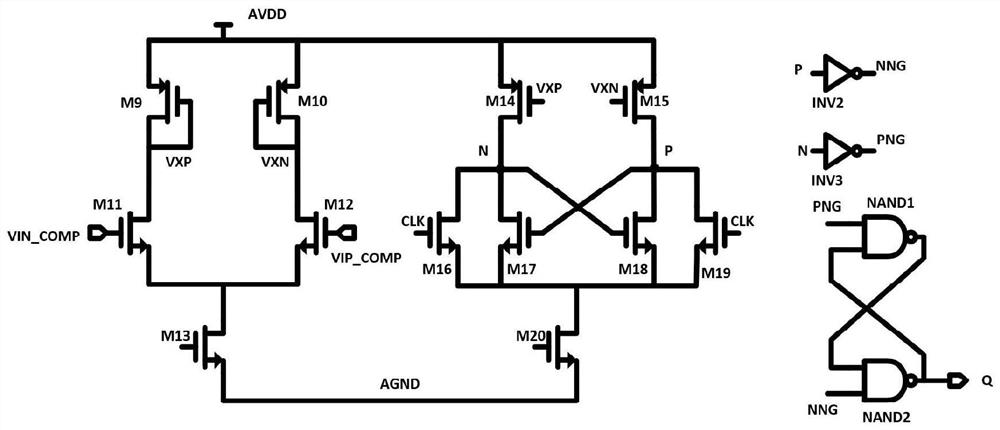

[0028] see figure 1 , figure 1 A structural diagram of a SAR ADC provided by an embodiment of the present invention specifically includes: a split capacitor DAC, an improved gate voltage bootstrap switch, a static secondary comparator, and a SAR logic circuit. Wherein, the analog signal input terminals (VIP, VIN) of the SAR ADC are connected to the input terminal of the improved gate voltage bootstrap switch, and the output terminal of the improved gate v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com