Chip simulation verification system

A simulation verification, chip technology, applied in instruments, computing, electrical digital data processing, etc., can solve problems such as reducing verification efficiency and increasing the workload of the verification process, reducing workload, enriching checkpoints, and improving verification efficiency and verification. quality effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

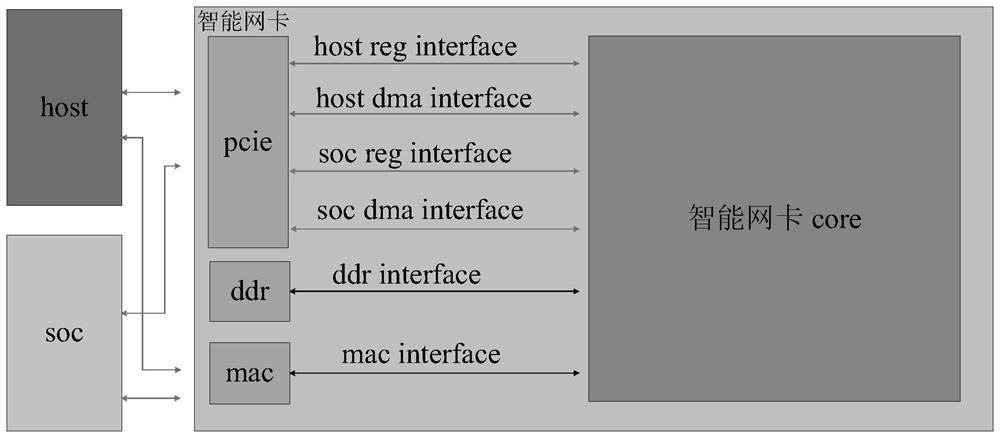

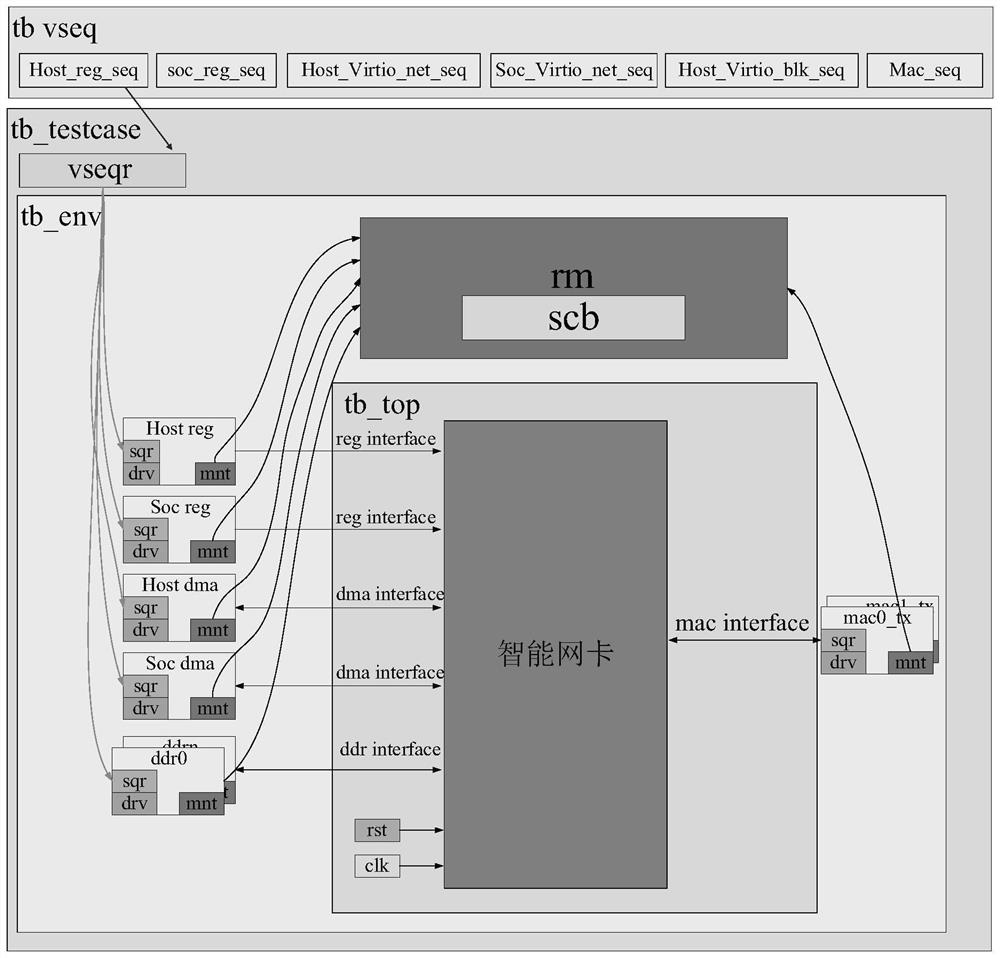

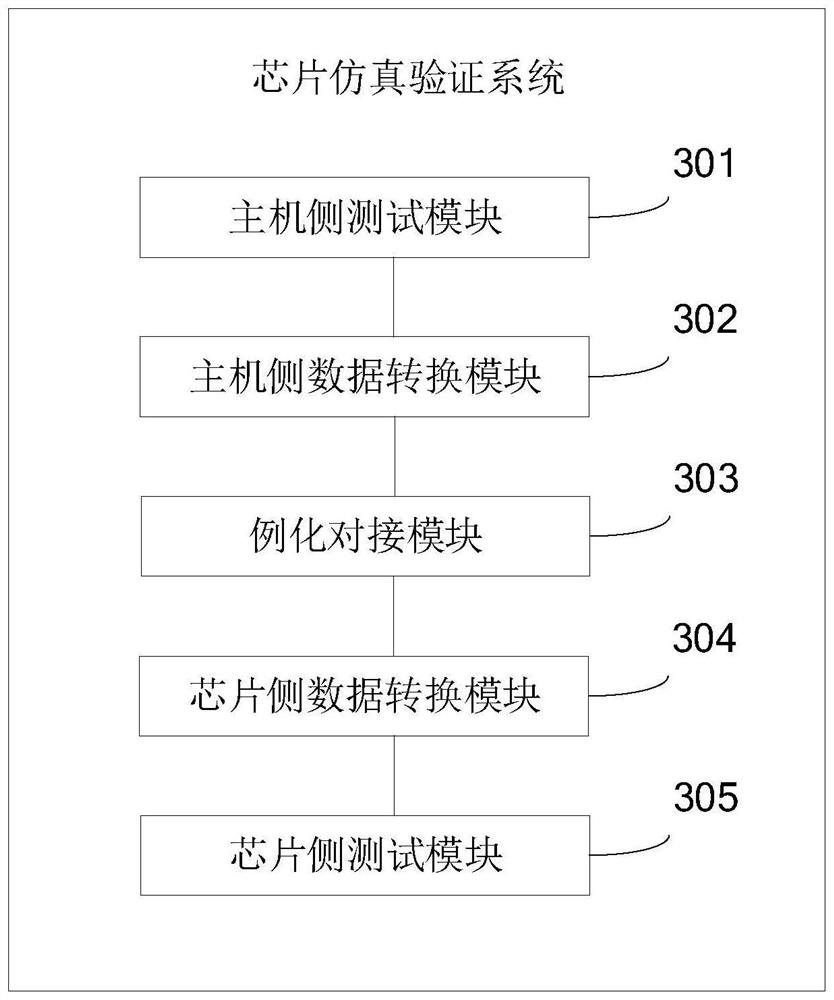

[0027] In order to make the purpose, technical solutions and advantages of the present application more clearly understood, the present application will be described in further detail below with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described herein are only used to explain the present application, but not to limit the present application.

[0028] First, briefly explain the terms involved in the embodiments of this application:

[0029] virtio protocol: virtio is an I / O paravirtualization solution, a set of general-purpose I / O device virtualization programs, and an abstraction of a set of general-purpose I / O devices in a paravirtualized hypervisor. It provides a set of communication frameworks and programming interfaces between upper-layer applications and various hypervisor virtualization devices (KVM, Xen, VMware, etc.), reducing compatibility problems caused by cross-platform, and greatly improving the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com