Novel packaging structure and manufacturing method thereof

A packaging structure and a new type of technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of decreased welding push-pull force, affecting the reliability of CSP packaged devices, etc. The effect of simple technical methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

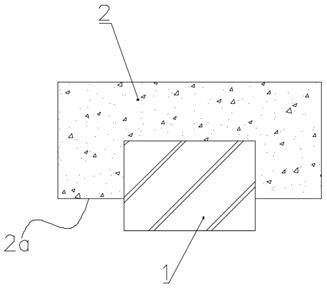

[0037] like figure 1 As shown, the novel packaging structure of the present invention includes a chip 1, which can be a positive chip or a flip chip. The outer surface of the chip 1 is covered with an outer packaging layer 2, and the outer packaging layer 2 includes an outer packaging layer arranged on the chip. 1. The top encapsulation layer on the top surface and the side encapsulation layer disposed on the side of the chip, wherein the bottom surface 2a of the side encapsulation layer on at least one side is 2 μm higher than the bottom surface of the chip 1 and not higher than half of the height of the chip 1 .

[0038] The comparison between the package structure in the first embodiment of the present invention and the traditional package structure soldered to the substrate is as follows:

[0039] Traditional CSP packaging structure: the adopted chip specifications are 760 μm long, 330 μm wide, 150 μm high, the top packaging layer thickness of the outer packaging layer is ...

Embodiment 2

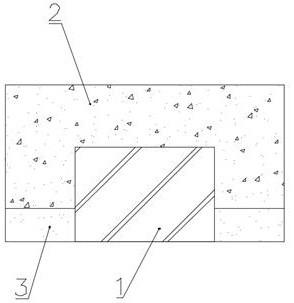

[0045] figure 2 Another structure of the packaging structure of the present invention is shown, which includes a chip 1, and a sacrificial layer 3 close to the side wall of the chip 1 is provided at the bottom periphery of the chip 1, and the height of the sacrificial layer 3 is not higher than half of the height of the chip. , the bottom surface of the sacrificial layer 3 is flush with the bottom surface of the chip 1 or lower than the bottom surface of the chip. As a more specific implementation of this embodiment, the thickness of the sacrificial layer 3 is not limited to be uniform, and it can gradually decrease from the center of the chip 1 to the outside.

[0046] An outer encapsulation layer 2 covering the outer surface of the chip 1 is provided on the upper surface of the sacrificial layer 3. The outer encapsulation layer 2 includes a top encapsulation layer arranged on the top surface of the chip 1 and a side encapsulation layer arranged on the side of the chip. The...

Embodiment 3

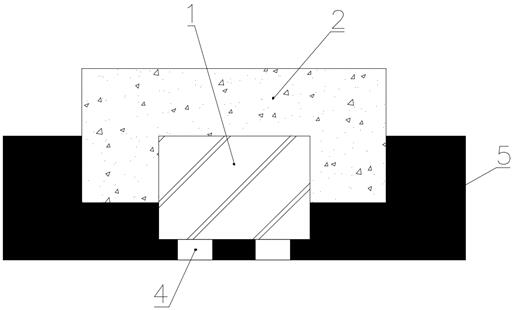

[0048] like image 3 As shown, in this embodiment, a chip 1 is included, the outer surface of the chip 1 is covered with an outer packaging layer 2, and the outer packaging layer 2 includes a top packaging layer arranged on the top surface of the chip 1 and a side packaging layer arranged on the side of the chip. layer, wherein the bottom surface 2a of the side encapsulation layer is not lower than the bottom surface of the chip 1 by 2 μm, and is not higher than half of the height of the chip 1 .

[0049] In this embodiment, the bottom surface of the chip 1 is provided with an electrode 4 that protrudes downward from the bottom surface, the bottom surface and the side surface of the outer packaging layer 2 and the bottom surface and the bottom surface of the chip are covered with a reflective layer 5, and the center bottom of the reflective layer 5 has two Electrode channel with exposed electrodes. The upper surface of the reflective layer is not higher than the upper surface...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com